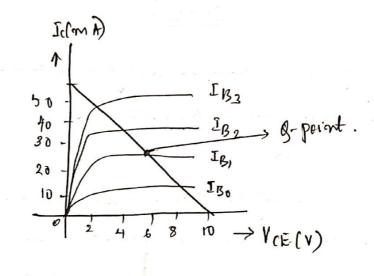

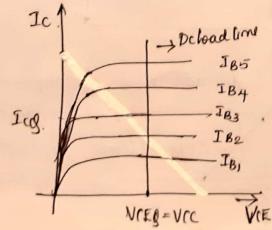

BJT Riasing: Application of DC Vollages to a transaction established a fixed level of Current and Vollage which establishes are operating point on the output characteristic.

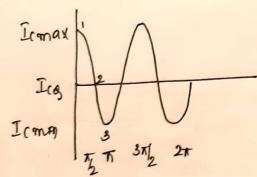

Sime the operating point is a fined point on the characteristic it is called guiescent point i've of-point for proper amplification.

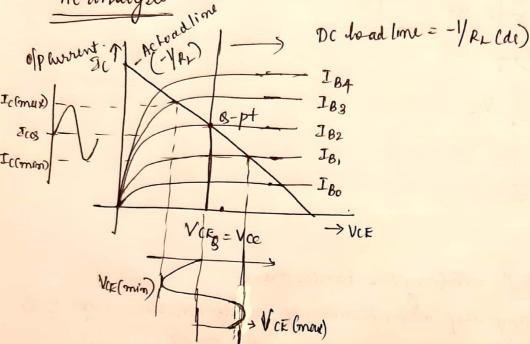

B-point its fixed on the middle of the active sugion.

The teransister can be beased in active or linear region bound on the following conditions.

The Bare-Enrither Junction Schoold be forward biased & collected Enritted Should be serverse briased

Teromeuster region of operation.

Active Region: B-E Junction is facusardhias and c-E Junction hyerse bias.

Saturation Rylon: B- Ejanction is farward him and C-Ejanction Farward burns.

cutt-off Region! B-E junction is Reverse brased of C-E junction reverse bear.

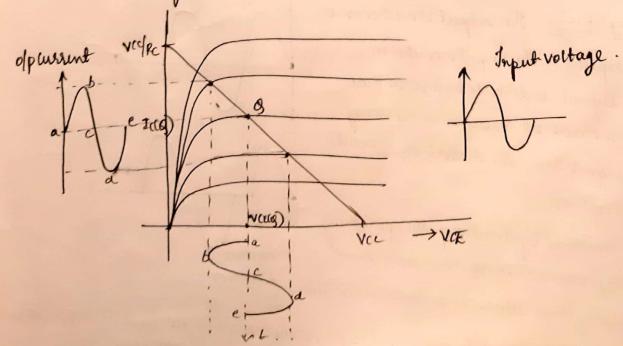

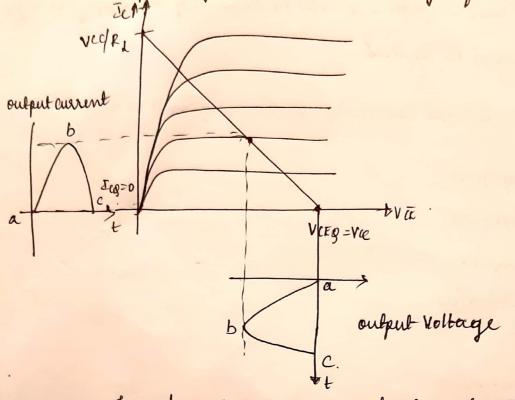

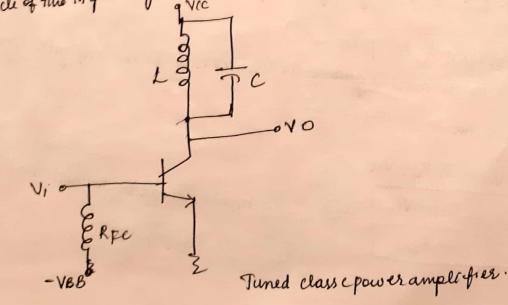

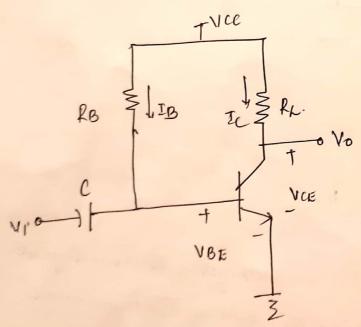

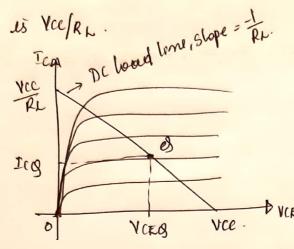

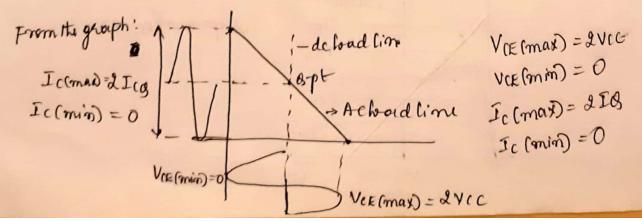

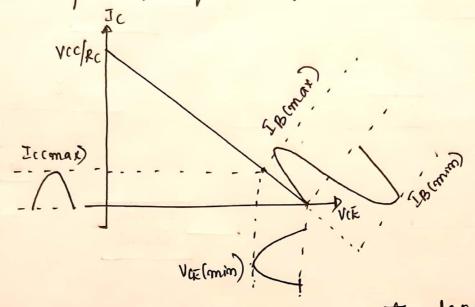

operating point or DC load line: The line called dc load line can be drawn on the characterstic of the transmister which supererents the applied load. The interection of the load line with characterster will determine the operating point

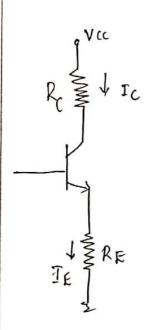

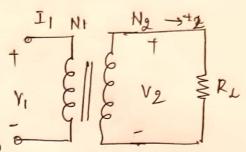

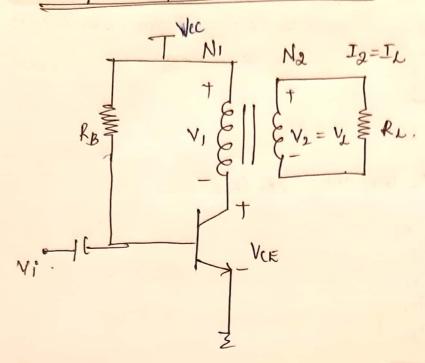

Consider C-R Circuit as Shonen below & Apply KNI to CKt

Biased transistor along with the characteristics with de doad hime analysis.

The VCE axis intercept can be found by choosing Ic=0, in Eq. 10

Vcc = VE

The Ic arus intercept can be found by choosing VIE =0 in EQTO

Equiation for the dc does have in the slope intercept from Eay 1)  $I_{c} = (-1/R_{c}) V_{c\bar{k}} + V_{cc/R_{c}}$

where the Stope is - /Rc while the intercept is Vcc/Rc. The intersection of This load home with the output characteristic results in possible operating Points. The operating point is Chosen around the middle of the load bre to provide on Equal Swing of Ic and VcE about the point.

### Types of Biasing

- O Fined bias of Base bias Cht

- 2 Emitter bias of Emitter Stabilized biasing

- (3) Voltorge dividu/ Current gain stabilized or Bindyandurt/universal bras

- A De kins with feedback.

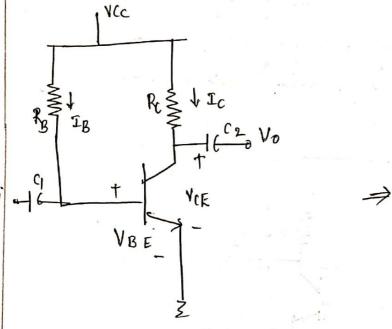

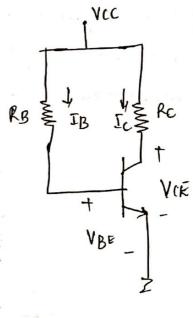

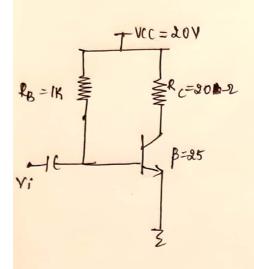

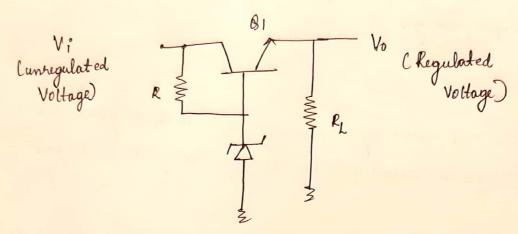

Fixed bias: Consider the Cht Shown below neglect C, & Ce for DC analysis

Fined bias cht with Capacitor

Dc kias

Apply KVL to Race to Emitter boop we get

$$\int_{\mathcal{B}} \mathbb{I}_{\mathcal{B}} = \frac{Vcc - VBE}{R_{\mathcal{B}}} \rightarrow \mathbb{O}$$

$$I_c = \beta I_B \Rightarrow \text{ Collector Current}$$

Sima the supply Voltage Vcc and VBF are constant on athe resistance RB is selected IB is also fixed then a the arount is called fixed bird cht

Apply KVL to C-E loop

For fixed hias CK+ VBR=VB, VE=0

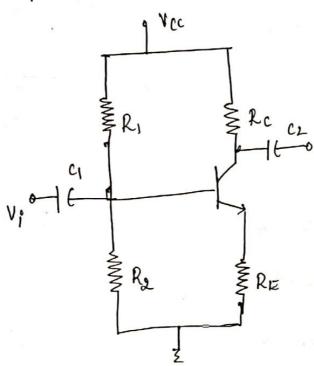

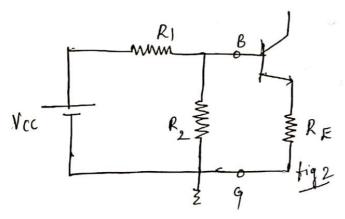

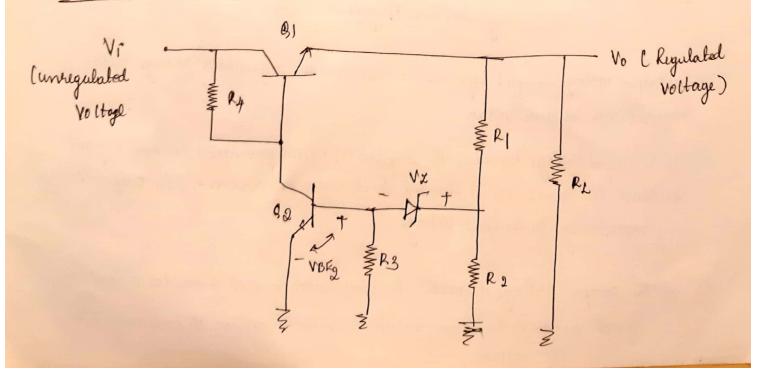

Voltage Divider Bias! In the fined bias and Emitter bias Circuit the guiescent values of Ic & Ver i've g-points is a function of de currents grown B of the transistor. W.K.T this current gain is sensitive to temperature and its values Keep Varying. A biasing art independent or less independent on p such as Voltage divider cricuit is desirable

Vtg divider bias or universal bias cut.

The voltage divider bios licuit Com be analyzed in two methods.

- > Fract Method

- > Approximate method.

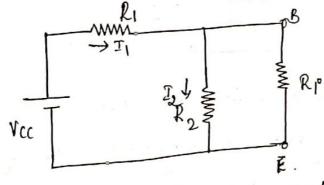

Enact Analysis: The input side of the CK+ i-e B-E CK+ of the figure es redrawn as shown in the figure below for de analysis.

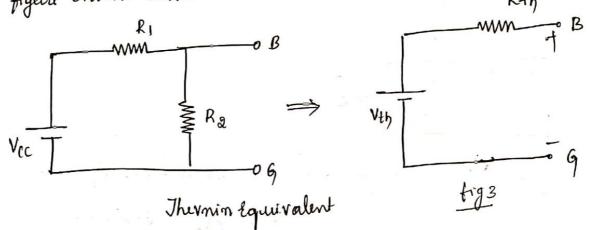

The thermin Equaralent of the Ckt Comparising of Va, R, & R, 2 of the above figure shown below.

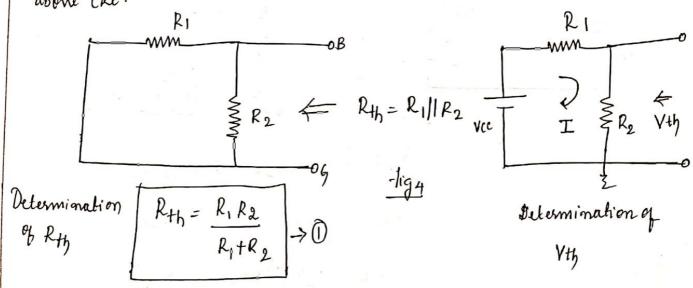

To find Rth i'e therenin resistance Rth, Vcc is reduced to Lurs i'n the abone Cht.

Vollage drap across Rg 113

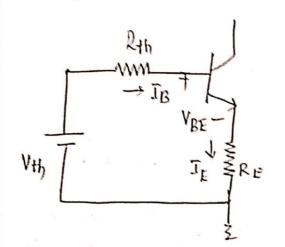

The fig 2 list ait is redrawn below to the thevenin Equalization Bog

Vth = IBRHH+VBE + JB(1+B)RE

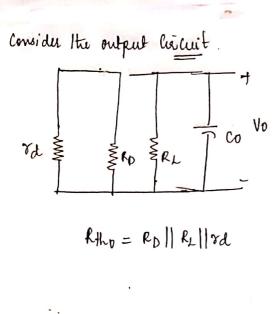

Considu C-E CKt

Apply KVI to CKT

VE = Voltouge across RE

In this Circuit negative feedback is provided through the Emitter resistance As a result Ic & VCE be come almost independent of B. For this reason Voltage divide bias is also called as <u>bela-independent Ckt</u>.

Approximate analysis: The resistana RE in the Emitter Ckt gets reflected as (1+B) RE in the base Ckt. Therefore the Ckt b/N base f ground in tigure Can be replaced by an Equality about resistance R1°=(1+B) RE.

Input licuit for Approximale analysis.

for the Ckt given above using KCL we get.

$$I_{i} = I_{2} + I_{B} \rightarrow 0$$

$$R_{i} = CI + \beta R_{E} \quad Sina \quad \beta > 1$$

$$R_{i} = \beta R_{E} \rightarrow 0$$

$$\widehat{J}_{B} = V_{B/R_{f}} \qquad \widehat{J}_{2} = V_{R/R_{2}}$$

$$\mathbb{P}_{i}^{*} = \beta R_{E} \geq 10 R_{2} \rightarrow \emptyset$$

Then IB & O.II2, Hence, IB Can be neglected in Eg D

I1 = Id

Apply KVL to CKt

$$VCC = I_1R_1 + I_2R_2$$

$$VCC = I_2(R_1 + R_2)$$

$$I_2 = \frac{V_{cc}}{R_1 + R_2}$$

Brop across R2 i.e VB = I2 R2

$$\int_{\mathbb{R}} y_{g} = \frac{V_{cc}R_{2}}{R_{1}+R_{2}} \Rightarrow 3$$

Observe the Expression for VB is identical to VII

Ramya K Auch perofusor Dept of ECE

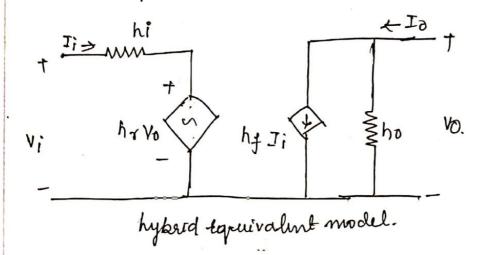

BJT transistor Modeling: In order to analyze the ac operation of a transistor amplified it is necessary to develop an ac Equivalent arcuit of a transistor. This ac Equivalent lixuit is called the model of a transistor.

The model of a transistor is a combination of circuit elements properly chossen the kest approximates actual behaviour of the transistor under specific operating conditions.

There are three models commonly used in the small signal ac analysis of transistor network

- 1. re model

- 2. The hybrid Equivalent model

- 3. The hybrid  $\pi$  model.

At low frequencies the Junction corparitorness of the transistor acts as open circuit due to Their high reactance due to their high relactionse at low frequencies small signal models donot consider the effect of Junction corpacitance

At high frequencies the Junction corpacitorness conduct appreciably due to Their low reactance providing feedbook porth from output to input in high frequencies Small signal models considers the Effect of Junction corpacitances.

he model: is a more practical model the important parameter he of This model is determined by the actual operating conditions nother than using data sheet values.

hybrid model: the transistor is modelled leaved on whole is happening at its terminals without regard for the physical process taking place inside the transistor

Azkrid T model: hybrid I model will provide a more accurate model for high frequency effects. This model its insed for a full frequency analysis.

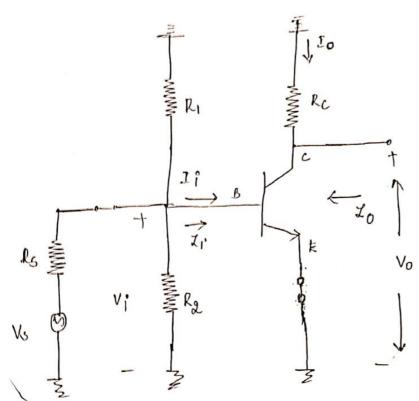

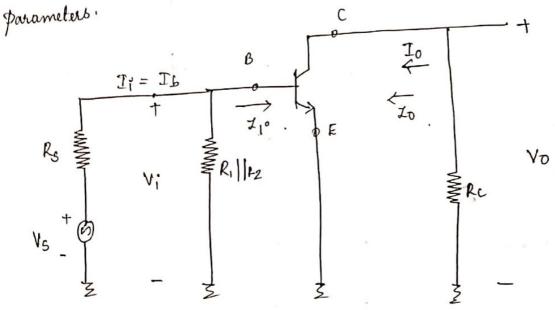

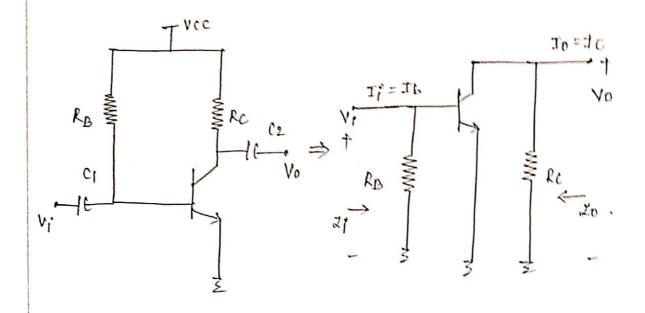

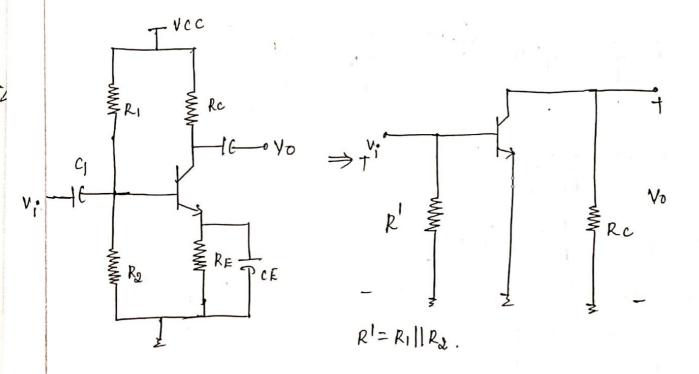

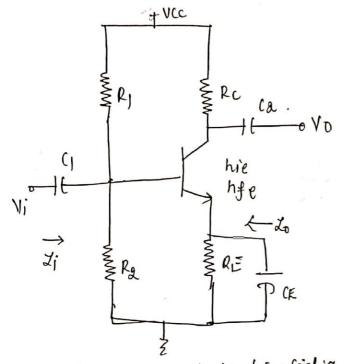

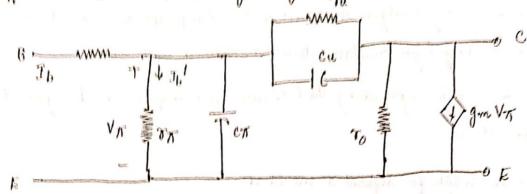

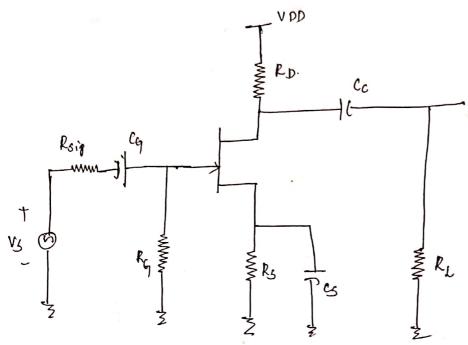

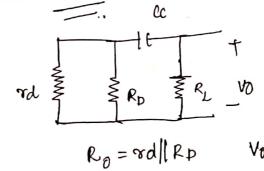

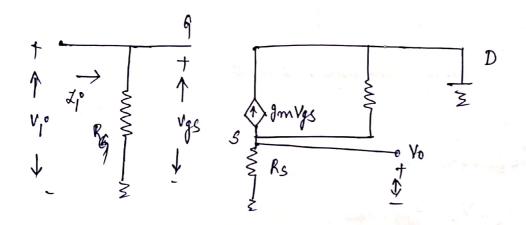

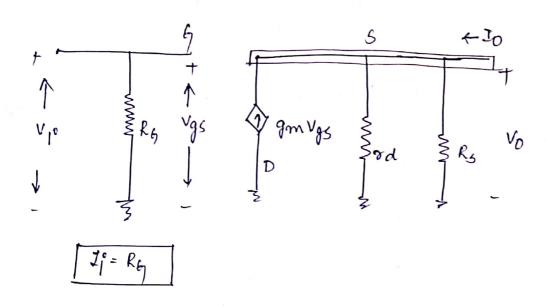

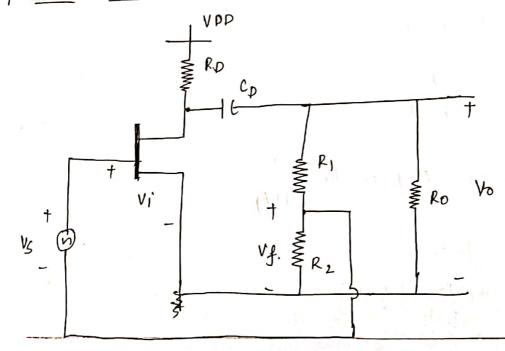

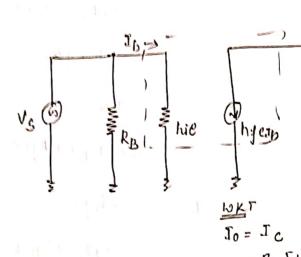

To demonstrate the Expect that the ac toperivalent avail will have on the analysis to follow lonsides the artifact as shown kelow.

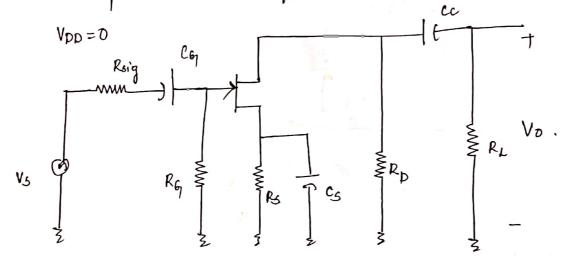

Since we are intrested only in the ac response of the circuit all the de Supplies can be replaced by a Loro potential Lapuivalent i.e. Vcc =0. The de levels i.e. vcc were important for determined the proper of operation, once determined the de levels can be ignored in the ac analysis of the network.

In addition the coupling capacitors c, and co and bypour capacitor CE were short circuited due to the small reactance, resulting in Short circuit the do biasing resistor RE.

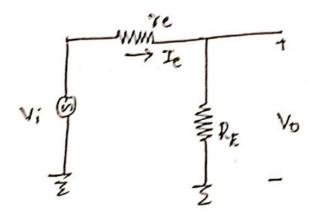

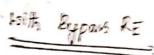

The resulting Equivalent with as Shown below.

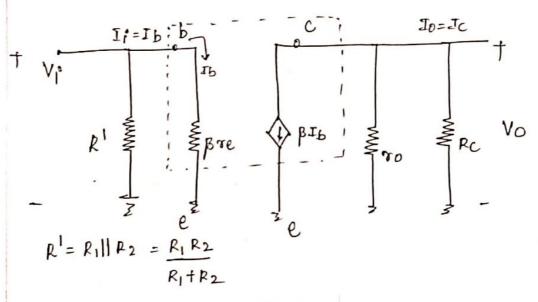

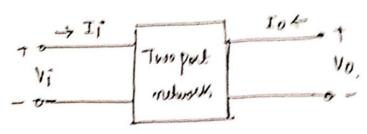

In ac Equivalent arcuit analysis we have to determine Zi, Zo, Av, A-T

Small Signal ac analyses.

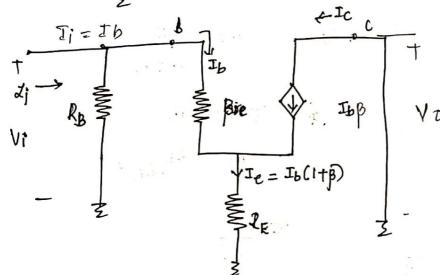

from the Circuit  $I_i = I_b$ ,  $I_0 = I_c$ . Setting all de Sources to Luro and replacing them by a Short Circuit Equivalent. Representing the network Replacing all Capacitors by a Short Circuit Equivalent. Redrawing the network in a more Convenient and clogical form.

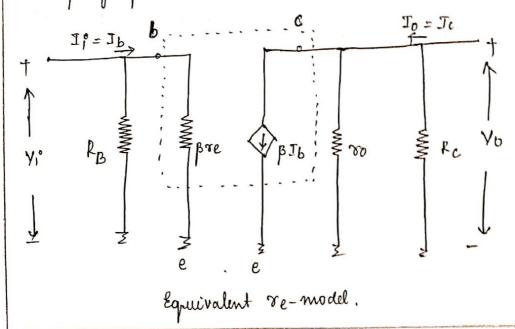

#### The re-transfer model:

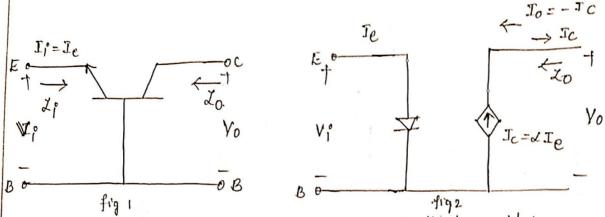

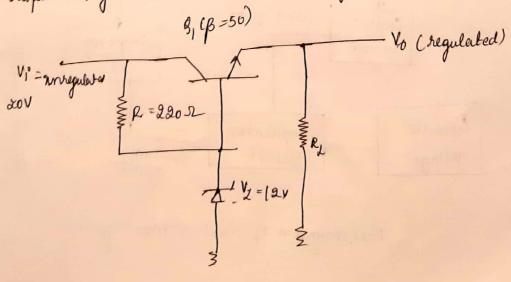

Common kove Configuration: Common kase BJT transistor has keen replaced by the remodel. The transistor action in this Configuration has keen replaced by a Single diale kelween builted and base terminals and Controlled Current Source between base and collector dorminals.

For ac response the diode can be replaced by its equivalent ac resistance. The ac resistance of a diode can be determined by the Expunction  $Tac = \frac{26mV}{ID}$ . where  $I_D$  is the dc current through the diode. Therefore representing  $T_C = \frac{26mV}{IE}$

Common-Base BJT transistor and re-model of the transistor

The Subscript e of re was chosen to emphasize that is the dc level of Emitter Current that determines the ac level of the resistance of the diode

Rece do the distribut that saids the the impatement output correlle of figures it should be fairly stribus.

Frank in producer for the dominion base configuration of downed for is

to a maximum of about 50 D.

Entent inverdance: For of primpedance if we set the signal  $\forall i=0$ , then  $T_{e=0}$  and  $T_{e}=\times T_{e}=\times \times 0$  a smalling in an open cracial topulvalene at the patrol demainals

" for sommon-buse configuration typical values of 20 over in Meguohm sunge" in general for the common base configuration ette input impedance is relatively small and output impedance is secrete high.

Voltage gain: from the network or frq 3.

$$V_{\theta} = -T_{\theta} R_{L}$$

$$= -(-T_{\ell}) R_{L}$$

$$V_{\theta} = T_{\ell} R_{L}$$

$$V_{\theta} = A T_{\theta} R_{L}$$

and Vi= Iiz 10 = Iezi = Iere

$$A_V = \frac{V_0}{V_i} = \frac{dJ/RL}{Je re} = \frac{dRL}{re} \quad if \ d = 1 \quad A_V = \frac{RL}{re}$$

$$A_{J} = \frac{I_{o}}{I_{p}} = \frac{-I_{c}}{I_{e}} = -\frac{\lambda I_{e}}{I_{e}} = -\lambda$$

$$A_{J} = -\lambda$$

- Eg (1) For a Common-base configuration with  $I_K = 4m A$ , d = 0.98 and an ac signal of dmv applied byw the base oud Emitter terminals.

- @ Determine the input Impedance

- B Calculate tu voetage gown if a load of 0.56 K-2 is Connected to the ofp termi-

- @ Find the output Impedance and Current goin

$$\rightarrow \mathcal{R} = \frac{26 \,\text{mV}}{IE} = \frac{26 \,\text{mV}}{4 \,\text{mA}} = 6.5 \,\text{D} \qquad , \quad \mathcal{L}_{1}^{\circ} = \mathcal{R} = 6.5 \,\text{D}$$

$$Av = \frac{Vo}{Vi} = \frac{168.86 mV}{2 mv} = 84.43$$

.  $Ai = \frac{Io}{I_0} = -2 = -0.98$

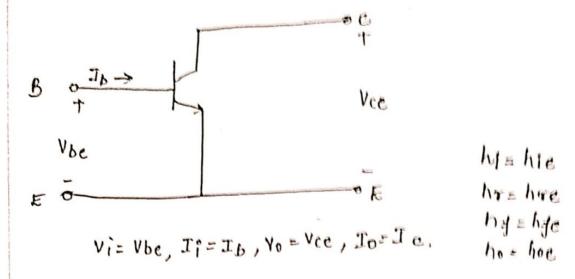

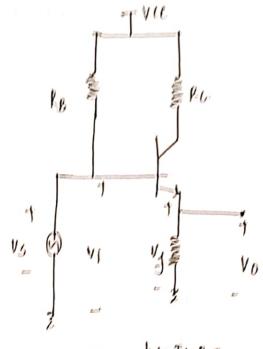

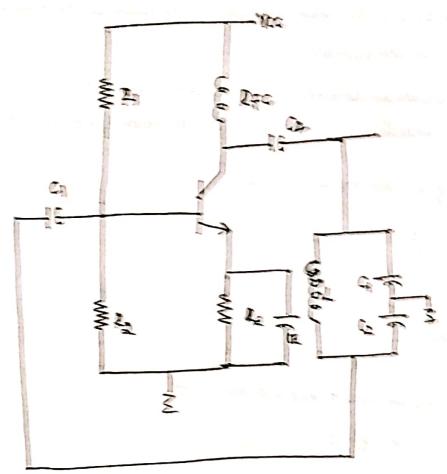

Common-Emitter Configuration: For Common-Emitter Configuration the input terminals are base and Emitter terminals and output terminals are Collector and Emitter terminals. Replacing the re Equil valent model the Controlled Current Source is Connected between the Collector and bosse ferminals and the diode between the bose and builter terminals.

In CE Configuration the base current is the input current where as output current us Ic

The current through the diode is therefore determined by

if Bis very much greater than 1 then 1+B=B Te = I6(1+B)

Common-smitter BJT tromuster and Approximate model CE Configuration

$$\frac{I_{1}^{\circ} = \frac{V_{1}^{\circ}}{I_{1}^{\circ}} = \frac{V_{be}}{I_{b}}$$

$$Vi = Vie = Ie ve = (Ie + Ii) ve = (Pib + Ii) ve$$

$$Vie = Vi = (Pib + Ii) ve$$

$$Vie = Vi = (Pib) Ie ve$$

$$I_{j} = \frac{V E_{k}}{3k} = \frac{(\beta + i) 3k}{3k} \pi e$$

for the lander-breaker landplaced on it defined by five range from for hundred shows to the Nahahan range with according a about 6x2 to 1x2.

entent improduire: From the people of constraint outs the country and

For CE Configuration Circuit of the applied digmal is let to size the Consult Ic=04 and of Empedant is

If rous ignored as in the re-model the subject impedance at defined by to = 0.2.

form. Av =

$$\frac{V_0}{V_i^3}$$

$$V_0 = -I_0 R_L$$

$$= -I_c R_L$$

$$V_0 = -\beta J_b R_L.$$

$$V_1' = I_1 I_2 = I_6 \beta^{T_6}$$

$$A_7 = -\frac{\beta^{T_6}}{\beta^{T_6}} RL$$

$$\frac{\beta^{T_6}}{\beta^{T_6}} Te$$

$$A_7 = -\frac{\beta^{T_6}}{\beta^{T_6}} I_2$$

Current gain

$$A_j = \frac{J_0}{I_1^{\circ}}$$

$$A_{I} = \frac{I_{C}}{I_{b}} = \frac{\beta J_{b}}{I_{b}}$$

Eg 2: Given B=120, IE=3.2 m A for CE Configuration with 80=00-2 determine Ii, Io, AV, AI with 2K2 docud resustor.

$$re = \frac{26mV}{3.2mA} = 8.125-2$$

$$Av = -\frac{RL}{re} = \frac{2K-2}{8.43} = -246.15$$

$$AI = \frac{I_0}{I_P} = \beta = \frac{120}{I_P}$$

For Common Collector Configuration: Replace the Emitter terminal with Collector and Viceversa.

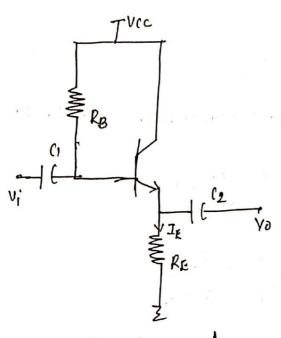

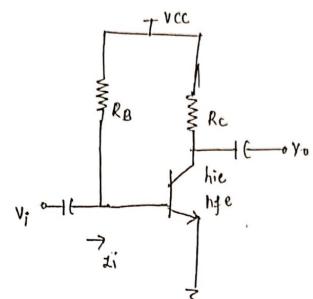

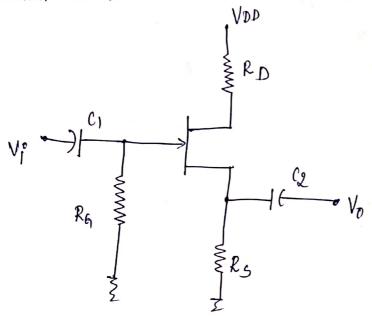

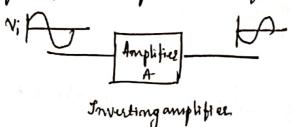

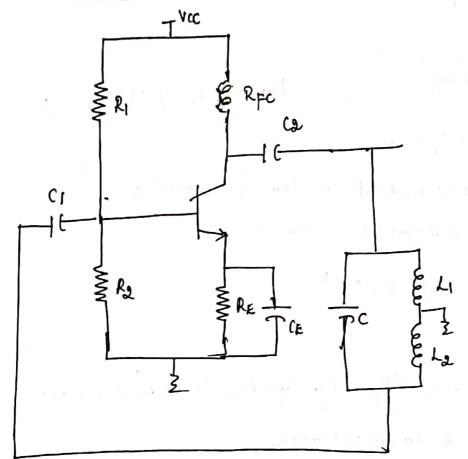

### Common-tmitter frized bias using re-model

Figure about shows the Common Emitter amplifies using the fixed bias the input Signal Vi is applied to ithe base of transister through input coupling capacitors of the amplified signal Vi is taken out the collector through the output loupling capacitor C2.

In order to perform the Small Signal ac ornalysis let als obtain the ac Equivalent around by reducing the de Souras Vecto Levo and short Civaciting the Coupling Corporator.

Input Impedance: from the circuit it is given by the parallel Combination

4. Ro and pre

Zi=fB//Bre

From Mis ornalysis of parallel elements that the stotal sessitione of two parallel reses too; it always less thouse the smallest and very to the smallest if one is much larger than other.

Re>pre

RBZ 10Bre

Ti=Bre REZIOBRE

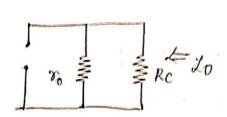

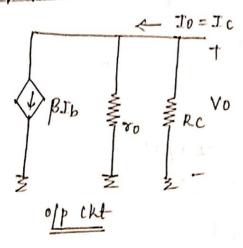

output impedance: The off impedance determined by Considering  $V_i^*=0$  when  $V_i^*=0$ ,  $T_b=0$ ,  $T_i^*=0$  susulting in open Circuit.

Voltage gain: Av = Vo/v; Consider the output araul.

$$V_0 = -I_0 \cdot RL$$

$$= -I_c \cdot ( \text{vo} || RC)$$

$$V_0 = -\beta I_b ( \text{vo} || RC)$$

promite i/p circuit Apply KVI to b-e bop we get

$$V_0 = -\beta \cdot I_b (roll Re)$$

$$= -\beta \cdot V_i (roll Re)$$

$$\frac{V_0}{\beta re} = -\frac{roll Re}{re}$$

$$Av = -\frac{roll Re}{re}$$

The negative Sign in the resulting Equation Av reveals that a 1800 phase shift occurs by the input our output signals.

Egs: for the network shown kelow determine re, Ii, Io, AV

IE 2.428mA ==

$$Av = -\frac{Rc}{re} = \frac{3K-2}{10.71-2} = -280.11$$

Av = - Rellro = -264.24

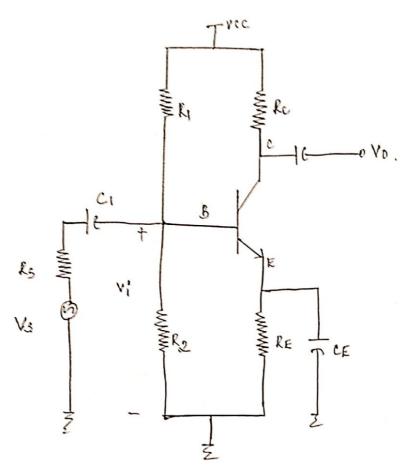

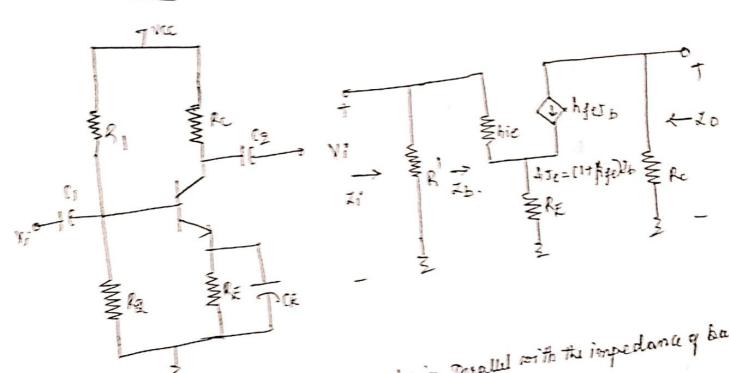

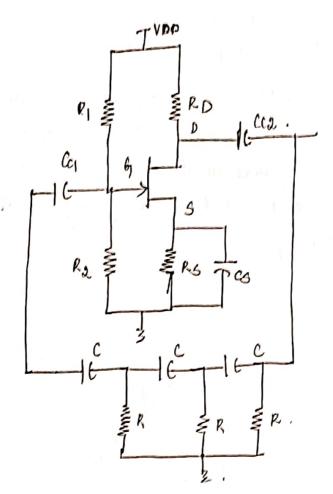

Voltage divider kias: CE Configuration using Voltage divider kias.

The ac input signal Vi is applied to the base of the transistor through the input loughing capacitor C. . The amplified signal Vo is taken out the Collector through the output Coupling capacitor C2. The Emitter bypass capacitor CE is used to prevent the closs of Voltage due to ac negative feed back through RE by Creating an ac ground at the Emitter.

At the New frequency the loupling Capacitors C1, C2 and bypass Capacitor CE us Short Circuited.

To perform the small signal ac analysis etter Equivalent CK+ by reducing Vcc to down and replace capacitors by short Circuit.

Re appears b/w collector and ground. RE parallel with Short Circuit of CE. But to low impedance across emitter RE is also short Circuited.

Input Impedornle: I'= R' | Bre

output Impedance: Lo,  $V_i^{\circ}=0$ ,  $I_i^{\circ}=0$ ,  $I_b=0$  therefore till BIb the Ckt is acting as open Circuit

Gain:

$$Av = \frac{Vo}{Vr}$$

$$V_0 = -\beta I_b (R_c | | v_0)$$

$$= -\beta \cdot \frac{V_i}{\beta r_e} (R_c | | v_0)$$

$$\frac{V_0}{V_i} = \frac{-(R_c | | v_0)}{\tau_e}$$

$$Av = -R_c | | v_0$$

Megative Sign indicates the phase shift b/w inputornol output.

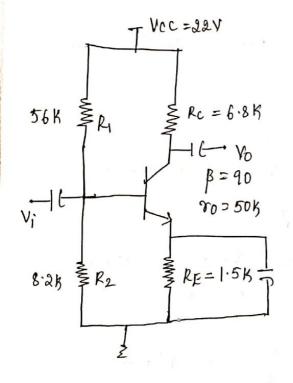

Eg:4 For the given n/w determine Li, Lo, Av. [ If rous not given consider ro=02 and neglect).

using Approximate analysis.

$$\frac{V_B = \frac{V_{CC} R_2}{R_1 + R_2} = \frac{22V \times 8 \cdot 2K}{56K + 8 \cdot 2K} = 2 \cdot 81V}$$

$$I_{E} = \frac{VE}{RE} = \frac{2 \cdot 11V}{1.5 \text{ KD}} = 1.4 \text{ Im A}$$

$$R^{1} = R_{1} || R_{2} = R_{1} R_{2} / R_{1} + R_{2} = 56 K || 8.2 K = 7.15 K \Omega$$

$$J_0 = \text{Rell ro} = 6.2 \text{Rell 50R}$$

$$J_0 = 5.92 \text{Rel}$$

$$Av = -\frac{1000}{80} = -\frac{5.9282}{12.442}$$

$$Av = -3.24-3$$

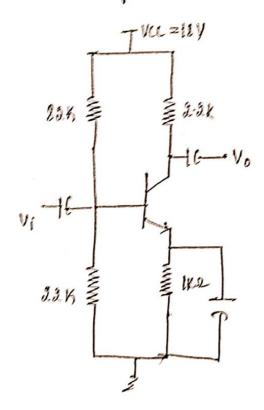

→ A voltage divides biosed amplifies has \$=100 and determine the Ii, Io, Av

100x1K2210x22K

100K Z 330K lendstier mot Satisfied.

use Exact analysis.

$$V_{th} = \frac{V_{cc} R_2}{R_1 + R_2} = \frac{18 \times 23 \times}{82 \times + 22 \times} = 3.807 \text{ V}$$

$$I_{B} = V + h - V B E$$

$$I_{E} = I_{B} C I + \beta$$

$$I_{E} = 26.25 u A C 101)$$

$$I_{E} = 26.25 u A C 101$$

$$Ay = -\frac{Rcl|Y0}{re}$$

$$Ay = -\frac{2 \cdot 2 \cdot K}{9 \cdot 81}$$

$$Ay = -224 - 2$$

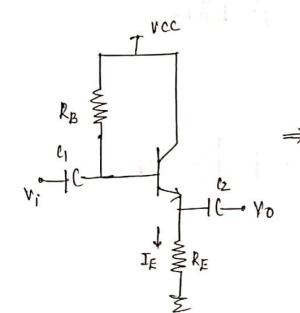

The output voltage is always slightly less than

the input signal due to du drop from base to

timites. The britter voltage is in phase with

the signal Vi

If it frequently used for Impedon a Matching if presents a high impedonate the input and a low impedance at the output which as opposite of the Standard fixed bear Configuration.

Substituting the re Equivalent lie and into the ac Equivalent on/w Imput Impedance: Apply KVL to the i/p arail we have

Ib = Bre+ (1+B) RE

11 = RB | 16

output Impedance: Consider Is = 1

$$T_b = \frac{VI}{I_b}$$

$T_b = \frac{T_c}{1+\mu}$   $\Rightarrow$   $T_c = (1+\mu)T_b$

$$\frac{Je}{1+p} = \frac{Vi}{Jb}$$

$$I_{e} = \underbrace{v_{i} (1+\beta)}_{I_{b}}$$

$$Te = \frac{Vi(1+\beta)}{\beta re+(1+\beta)RE} = \frac{Vi \times Vi}{\beta (re+RE)}$$

$$Vi \quad \text{de+RE}$$

$$Av = \frac{RE}{re+RE}$$

To find to: Yi=0

$$h_y = \frac{v_0}{V_i}$$

Apply Vollage divides sule to to cut

$$I_i = V_i$$

$I_0 = -V_0$

$RE$

$$= \frac{\text{Volle}}{\text{Vil}_{X}}$$

$$AJ = AVZi$$

$RE$

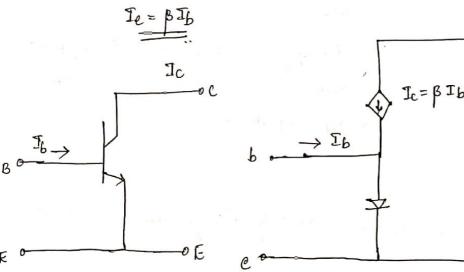

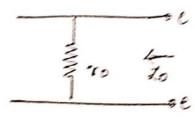

Consider the Lun good reducers, To develope the hypered Exquir valued model of these part network.

lander Ji and Vo are independent Variables and Vi and Io our dependent Variables

$$V_i = h_{i1}I_i + h_{i2}V_0$$

$I_0 = h_{21}I_i + h_{22}V_0$

The garameters his hiz, he and has are called hybrid parameters of h-parameters. It is hybrid because the parameters are mix of impedance, admittance and dimensimber with

$$h_{11} = \frac{V_i}{I_i} |_{V_0 = 0} \Rightarrow J_{npulinpedance} = h_i$$

$$h_{ij} = \frac{\Lambda_i}{\Lambda_i} \Big|_{\underline{I}_i = 0} \Rightarrow \text{ former supposition the entropy } = \mu_{ij}$$

$$h_{al} = \frac{I_0}{I_1} |_{V_0 = 0} \rightarrow f$$

among voltage transfer matro. = hf

#### From the Equation

hi Ii - represents the voltage drop across the impedance hi hovo - represents a controlled voltage source.

1 j Ii - represents a Controlled Current sousce ho vo - represents the averent through the admitton a ho.

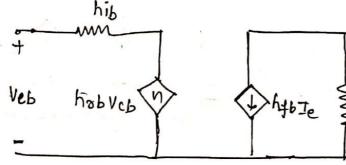

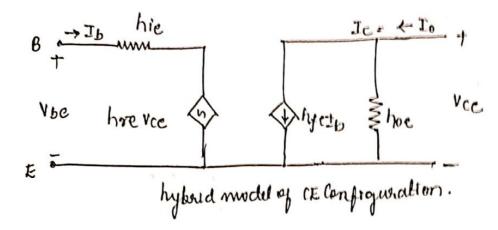

## Hybrid model of (Blonfiguration)

$$hi = hib$$

$hr = hrb$

$hf = hfb$

$ho = hab$

Ic = hfbIe + hob Vcb.

Veb = hib Ie+ hab Vcb

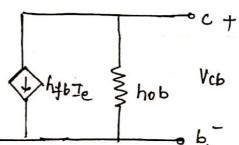

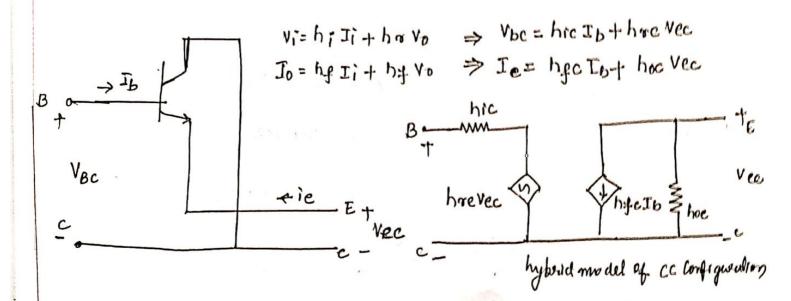

# Hybrid model for CE Configuration

$$V_i = h_i I_i + h_0 V_0$$

$\Rightarrow$   $V_{bc} = h_i e I_b + h_0 e V_{ce}$

$$I_c = h_f I_i + h_0 V_0$$

$$I_c = h_f I_0 + h_0 e V_{ce}$$

Hybrid model for ec Configuration

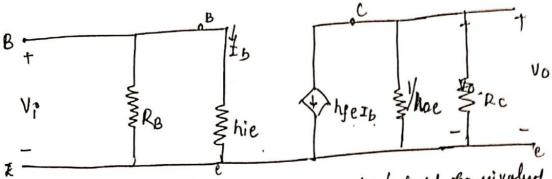

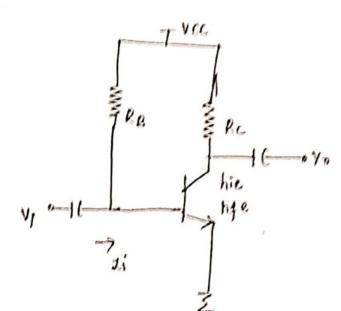

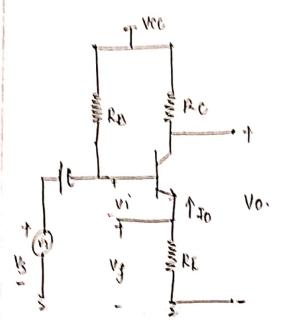

Figure Shows the Promptified wiling fixed beas. The actimput Signal Visis applied the the last of Lovernettes attrough the tagent Coupling capacidor C, the amplified dignal Vo is laken at the collector through the output Coupling capacidor C.

For small signor ac analysis the de Lource vec will be loqued to down short circuit the bupling capacitos (15/2.

Re appears b/w base and ground Rc b/w whector and ground.

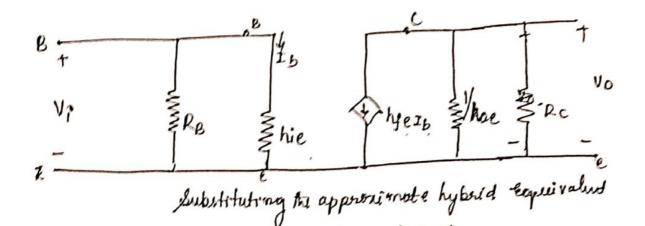

Substitution of the approximate hybrid topeivalud Circuit in ac topeivalut N/N.

= -hfe ID RL

= -hfe ·

$$\frac{Vi}{hie}$$

Av =  $\frac{Vi}{hie}$

Av =  $\frac{Vi}{hie}$

$\frac{Vi}{hie}$

$\frac{Ay = -hfe}{hie}$

$\frac{P}{hie}$

$\frac{Vi}{hie}$

$\frac{Ay = -hfe}{hie}$

$\frac{P}{hie}$

$\frac{P}{hie}$

$\frac{P}{hie}$

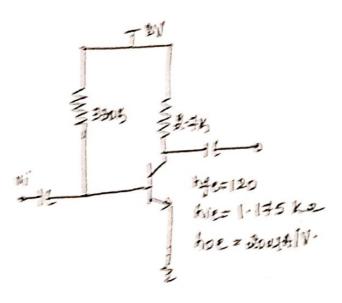

Figure Shows. Str. (Earnplifie, suring fixed blas. The a c imput signed Visic applied to the base of Lovenster structured the imput Coupling capacider C, the amplified signal Vo is lower at the collector through the output coupling capacider (s.

For small signal ac analysis the de source vac will be Expend to down short around the bespling capacito? (13/2.

Pe appears blu base and ground Re blu collector and ground.

Ii = Rellhie

Zo = Rell /hoe

Gain! Ay = R= Rell /hoe from ext

Yo= -IoRL

= -IcR

$$A_{V} = \frac{v_{0}}{v_{i}} = -\frac{1}{4}e\left( \ln 11 \frac{v_{0}}{v_{0}} \right)$$

hie

$$A_{i} = \frac{I_{0}}{I_{i}} = \frac{h_{2}e^{2}b}{I_{0}} = \frac{h_{2}e^{2}b}{I_{0}}$$

For the office defending to the , he , hi

$$J_1 = R_B || hie = 330 k || 1-145 k L = 1-14 k - 2$$

$T_0 = || have = \frac{1}{3000 \text{ MeV}} = 50 k D$

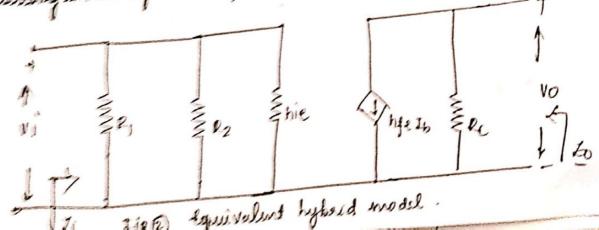

No Frage dividue Configuration: For the voltage divide bias configuration The Survey dividue bias configuration I = 0,1/42

( without bypass RE)

Fig () Voltage di vides bias Configuration

The small signoil parameter here views often too small to be considered 50 that input runstance is Just hie often the output runstance hoe is often large compared with the collector resistor Rc and its Effects can be ignored.

Input impedance! (Li): The input impedance is the possible combination of bias heristock R15 ed R1=R111 R2

RI farallel with hie

output impedance. As hell ( \$ Ib) is an ideal current generator with

infinite output impedance

Vollage gaim (A): The negative sign indicales phase inversion of the output.

$$\Delta r = -\frac{hfe}{hie}Rc$$

Current gain: AI = Io Ii

using current di vi des sule To Ii R!

$$IiR' = Ib$$

$$R'thie$$

$$\begin{bmatrix}

I_0 = -h_f e & I_b \\

I_b = -h_f e

\end{bmatrix}$$

$$\frac{\overline{J}_b}{J_i} = \frac{RI}{R! + h_i e}$$

$$A_{I} = \frac{I_{0}}{I_{i}} \times \frac{I_{b}}{I_{b}} = -h e \cdot \frac{RI}{Rfhie}$$

The injust impedance of is the base resident in Jarable with the impedance of base

$$\mathcal{I}_b = \frac{V_i}{I_b}$$

Apply RVI to the base to five the

$$v_i = J_b (hie + (1+hf))^R$$

$v_i = J_b (hie + (1+hf))^R$

$$\frac{d}{dx} = \frac{V_i}{I_b}$$

### Emittee follower Circuit

$$I_b = \frac{V_i}{I_b}$$

hie is very much small compared with (Ithfe) RE So Neglect hie

$$J_b = \frac{V_i}{J_b} \rightarrow 0$$

$$J_b = \frac{J_e}{1 + h_{fe}} \rightarrow 2$$

Compare formation (1) + (2)

$$\frac{Vi}{z_b} = \frac{z_c}{1 + h + c}$$

hielithige Vi D RE VO

Apply vollage divider Auto to the out

$$A_{V} = \frac{Ve}{V_{i}} = \frac{Re}{R_{F} + his/14hfe}$$

Hybrid A model: Hybrid A model its more accurate model for high frequency Effects used for put progressing analysis

Giacost el or hybrid A modo high froquency-bornistor Small Signal as Equivalent Circuit.

All the Capacitoss that appears in the above figure are stray parasitic Capacitoss between the various junction of the device.

At high frequency all capacitive Effects will come into play, at how frequency all Capacitance acts as open accuit.

ET represents tu diffussion capacitome of forward bias of Base-Emitter Junction Cu bransistion capacitana due to reverse beas of collectoranol Base Junction.

The resistance of includes the base contact, base bulk and base spreading resestance level first is due to adual connection to the base second include the resistance from the External terminal to active region of the transcriptor. Last includes the actival resistance within the active kase region.

of = Bre

The is very large rusis former and paramides a feedback path from disput to i/p

Circuits in the Equivalent model. To represents the output heritana across the load.

For low to midfrequency analysis the effect of the stray capacitive effects can be ignored due to very high reactance devels associated with Each.

To is very small can be replaced by short arenit runis largest can be ignored for many applications.

Typical data Sheet values for hybrid 1 model us

$$\gamma_0 = \frac{1}{h_0 e}$$

CB hybrid parameter in terms of CE hybrid parameter

cc hybrid parameter in terms

$$hoc = hoe$$

.

IN (1) Explain and obtain the re-math for to and to briggeration of interpretation and obtain the re-math for to and to be put trapsperse of on (2) represented when you vollage goin, if projections and output trapsperse of one (2) repeated bios using hybrid and remodel

3) Don't ve an Engrussian for voltage gain, if prinquitano and out put Impotarno of an Emittee forthem for the matter out hybrid passines et.

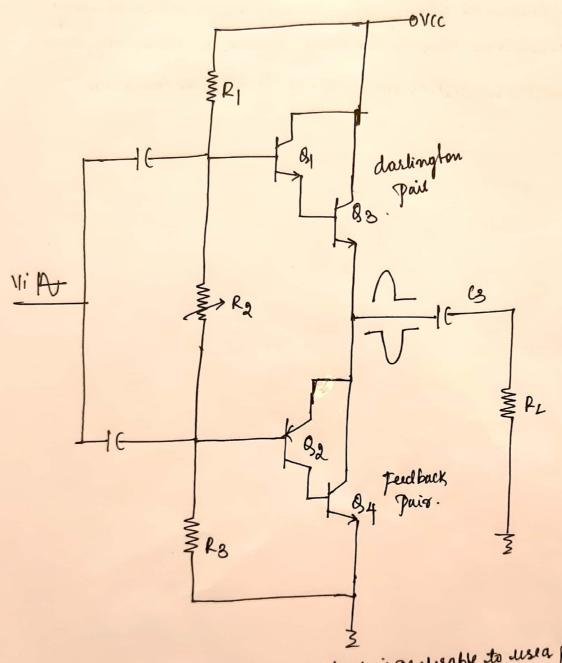

(A) with necessary expuisablest crush disapram othern the Extens Voltaguered consents for a Barlington connection.

The point of the Spainter Can be obtained from the State characteristed by the Esphain time that characteristed by the francistes (Englasin Systems begins of Englash Systems of Englash

A: Just using complete hybrid tapunvalent model for Tempert-System I transitud desire expressions for AI, AV, Is, ito.

(3) Busine Expount on fee of , it of Avi A I for a Nollange devider bein les we fet of BJT.

(b) sexime hoposomoter sound have derive hoposometer model for a ct et et .

(f) A voltage sown of regligible internal suitemedrives a tememen collector townsites a pasametral townsites amplific. Its sound suitament is associated townsites amplific. Its sound suitament is associated to the = 10001, hac=1, hec=50, hec=3544/V ditument to the first of the sound his = 10001, hac=1, hec=50, hec=3544/V ditument to the first of the sound to the first of the sound to the first of the sound to the first of the firs

(β) for on lower by the polythouse court of the one lower polythouse court of the low

Kanya.k. Acet profused, BGSIT, ECE

Logarithms: To define the relationship between the Variables of a logarithmic function Consider the following mathematical Equations.

$$a = b^{\alpha}$$

$\alpha = log_b a$

The Variables a, b and a are the some in Each Expectation If a is determined by faking the base b to the a power the Same a will result if the log of a torken to the base b

For Example Consider if b = 10 & x = 2

$$a = b^{\alpha} = 10^{2} = 100$$

$\alpha = \log_{10} a = \log_{10} 100 = 2$ .

For the electrical/electronics industry and in fact for the Vast majority of Scientific research the base in the dogorithmic equation is chosen as either 10 or the e=2.718 dogarithms taken to the base 10 are referred to as Common logarithms where as logarithms taken to the base e are referred to as natural logarithms.

Common logarithm &= log10a Natural logarithm y= logea.

The two are related by the topulation loge  $a = 2.3 \log_{10} a$ .

Some properties of Common logarithms to any base

$$\log_{10} 1 = 0$$

$$\log_{10} \frac{a}{b} = \log_{10} a - \log_{10} b$$

$$\log_{10} \frac{1}{b} = -\log_{10} b$$

$$\log_{10} ab = \log_{10} a + \log_{10} b.$$

Decibals: The term decibel has its origin in the fact that power and audio levels are related on a logarithmix baris.

For the standardization the bel (B) is defined by the following laperation relating the

The kel was too longe unit of measurement for practical purpose so the decibel (dB) is defined such that 10 decibels = 1 kel.

The terminal rating of electronic Communication Equipment is lommonly inducibels. The decibel rating is a measure of the difference in magnitude b/w thus power levels for the Specified divid / Hub/posses/level, terminal (output) power (p2) three must be reference power level (p1).

The reference level is generally accepted to be Imw, 6 mw Standard of earlier is applied. The resistance associated with Imw power level is 600 D chosen because it is the Characterstic impedance of audio transmission lines.

There builts a Second Equation for decibels that its applied frequently. It can be described by the following figure.

Let  $V: f_{n,i}(x) = V_1 V_1 + V_2 V_3 V_4$

$$v_i^{\dagger} \xrightarrow{R_i^{\bullet}}$$

for  $V_i$  Equial to Some value  $V_1 p_1 = V_1^2/R$  where  $R_i$  is the input resistance of the System of  $V_i$  is increased or decreased to Some Poul.

V2 then  $p_2 = V_2^2/R_i$ .

Gab = lo log 10

$$\frac{P_2}{P_1}$$

= lo log  $\frac{V_2^2/R_1^2}{V_1^2/R_1^2}$

Gab = lo log 10  $\frac{V_2^2/R_1^2}{V_1^2/R_1^2}$

AB

$$\int G dB = 20 \log_{10} \frac{V_2}{V_1} dB.$$

For Example the magifude of the orwood Voltage gavn of a cascaded System us given by  $|Av_T| = |Av_1| |Av_2| |Av_3| - |Av_n|$

Applying the proper logarithmere relationship results in

Pelm: The i/p power to a denice is 10,000 w at a Voltage of 10000 The output power is 5000 and output impedance is 20-2

- O find power gain in decibels

- @ find the voltage gain in decibels

$$= -10 \left(1.30\right) = -13.01 dB$$

$$61v = 20 \log_{10} \frac{v_0}{v_1} = 20 \log_{10} \frac{\sqrt{RR}}{1000} = 20 \log_{10} \sqrt{\frac{500 W \times 20-2}{1000 V}}$$

=

$$20 \log_{10} \frac{100}{1000} = 20 \log_{10} \frac{1}{10} = -20 \log_{10} 10 = -20 dB$$

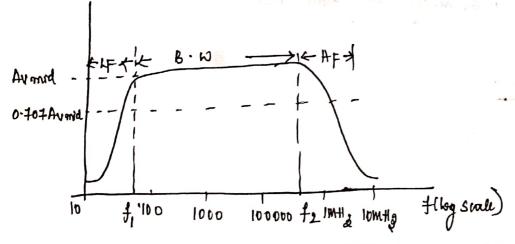

Frequency response is the plot of Magnitude of Nottage gain as a function of frequency In transactor amplifies the low frequency response is analysed by coupling capacitors and bypass capacitors. The high frequency response is analysed by transactor parastic capacitances & stray wiring capacitance

### General frequency Consideration

At high frequency > Stray wining capacitor & By pass capacitors Effect the signal At high frequency > stray wining capaciton a and parasitic capacitance lifed the signal

#### Frequency response of RC Coupled Amplifier

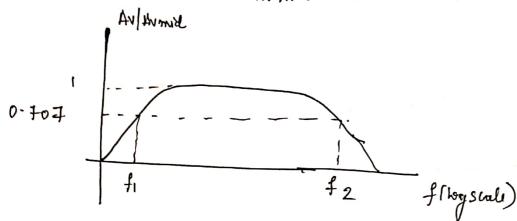

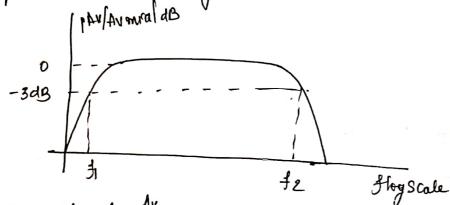

The frequency response of an amplified is the plot of the magnitude of VoHage gain as a function of frequency. Figure below shows the frequency susponse of Rc loupled amplified

X-anis is frequency which is usually logarithme seals to fascillitate low frequency to high frequency

Y-axis is magnifude of gain /Av

Frequency response of Rc Coupled amplifier.

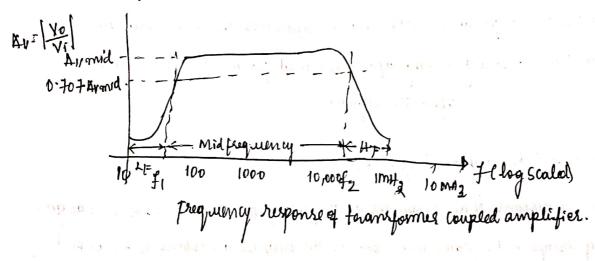

# Frequency response of transformer coupled amplifier

At low frequencies the gain drops due to small value of XL. At f=D

$$X_L = 2\pi f - L = X_L = 0$$

Therefore low frequency susponse is due to small value of of

At high frequencies gain drops due to Stray capacitore b/w turns of primory and secondary windows

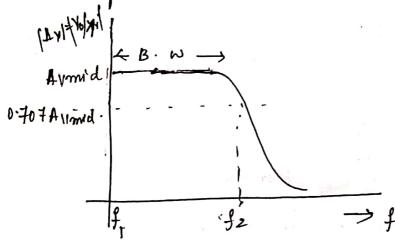

### Treguency response of direct coupled amplifies

Direct layed amplifies donot cuse coupling and bypass Capacitass As a result there is no drop in gam at low-frequencies the frequency hisponse Curry is flood upto the appearant of frequency Gain drops of high frequences due to the dente internal capacitan us and the stray withing lapar famels

# Normali ded gain frequency plot

In Communication application such as audio and vice it is more useful to supresent the mormalised gain in dB

At midband Av => the normalized mid band gown is Egyewel to 1

The normalized gain at outl-off frequencies 0-407 Avmid =0-70]

Normalized decibal Hyggain is Av - 20 hog 10 (Av mid)

Normalized decibel V+g gain in mid band is

### Half power frequencies and Bandwidth

The frequencies of and 12 at which the gain is 0.707 Avond are called cut off frequencies or Corner frequencies or break frequencies of is called the lower art of frequency and 12 the upper and of frequency.

The kand width of the amplifies is go ven by.

The output voltage in the midberns of

$$\left[A_{V}\left(mid\right)\right] = \left|\frac{V_{0}}{V_{1}}\right|$$

output power in the medband is

$$Po(mid) = \frac{|Vo|^2}{R}$$

The output Voltage at autt-off frequencies is

The output power at outl-off frequencies is

The olp power of cuttoff prequencies is holf the mid band power output for this reason found by are also called the half power frequencies.

Bysesing vig divides rule

$$\frac{V_0}{V_1} = \frac{R}{R - i \times R}$$

$$A_{Y} = \frac{R}{P}$$

$$P(1-j\frac{Xc}{R})$$

$$A_{\gamma} = \frac{1}{1 - j \frac{xc}{P}}$$

$$|Av| = \frac{1}{1 + \left(\frac{xc}{R}\right)^2}$$

Affer

$$x_c = 1 = 1 = \infty$$

arfe  $x_c = 1 = \infty$

At

$$f=\infty$$

$x_c = \frac{1}{2\pi fc} = 0$

$$2\pi fc \quad 2\pi(\infty)c$$

Scanned by CamScanner

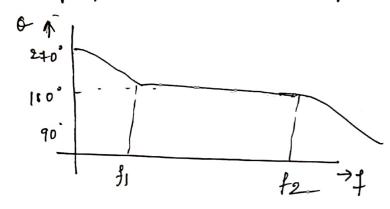

Phaseangle plot: A stage & Coupled amplifies introduces a 180 phase slutt blu ilps of p signals in the mid band regron.

At low frequencies Volag VI - by an additional angle OI

At high freezewaries Volende by VI - by an additional angle of

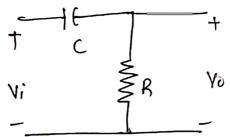

Low-frequency analysis: In low frequency analysis the response is like a high pass fitter high pass fitter as shown in graph. Therefore it can be modeled as high pass fitter

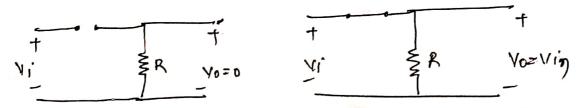

Capacitive reactorna

At f=0,  $X_c=\infty$  at low frequencies capacitor acts as open what :.  $V_0=0$ At  $f=\infty$ ,  $X_c=0$  at high frequencies capacitor acts as short Ckt...  $V_0=V_{ig}$

.. Mid band and high frequency response of Coupling & bypass Capacifors are Same

> When the Capacitive readance equals to the resistance ie & C = R

$$|\Delta_{V}| = \frac{1}{\sqrt{1 + \left(\frac{x_{C}}{R}\right)^{2}}} = \frac{1}{\sqrt{2}}$$

$$= \frac{1}{\sqrt{2}} \times 1 = \frac{1}{\sqrt{2}} |Avmrd|$$

Corresponding magnitude in dB

IAVIdB = 20 log 1/12 = -3dB The above condition is solutified only for cull-off frequency

At cull-of frequency

$$\begin{array}{c} R_{C} = R \\ = R \\ 2\pi f_{C} \\ \hline f = 1 \\ 2\pi R_{C} \end{array}$$

where f is hower supper cuttoff frequency denoted by f

\* Let us consider

$$\frac{x_c}{R} = \frac{1}{2\pi \epsilon R} = \frac{1}{2\pi \epsilon R} \cdot \frac{1}{f}$$

where f is the general frequency

$$\frac{x_{C}}{R} = \begin{bmatrix} \frac{1}{2} \\ \frac{1}{2} \end{bmatrix}$$

$$|Av| = \frac{1}{\sqrt{1+\left(\frac{x}{R}\right)^2}}$$

O, is positive Voleads Vi by an angle o,

Bode plot of low frequency response

$$|A_V| = \frac{1}{\sqrt{1 + \left(\frac{f_1}{f}\right)^2}}$$

how frequency response of HPF. Recuicit

| f     | filf | Av = -21 | olog ( 41/4)        |                                         |

|-------|------|----------|---------------------|-----------------------------------------|

| f1/10 | 10   | -20dB    | at 10 <sup>14</sup> |                                         |

| £1/4  | 4    | -12 dB   | N":                 | A change in frequency by a factor of    |

| filz  | 2    | - 6dB    |                     | A change in frequency by a factor to is |

| ના    | 1    | odB      | Ą                   | Equal to one de cade.                   |

|       | 3 -  | fi/4     |                     | 2 frequency response                    |

Slope = -6dB/octave or 20dB/decade.

Bode plot for low frequency region

-12

-15

-18

-20

-21

is

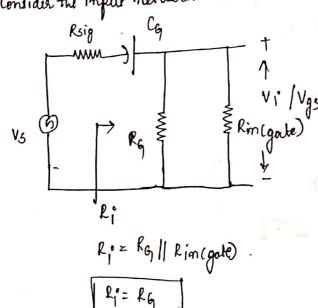

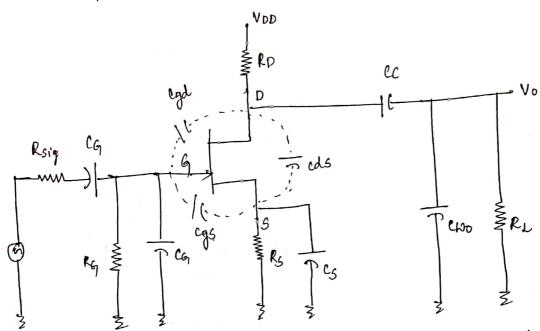

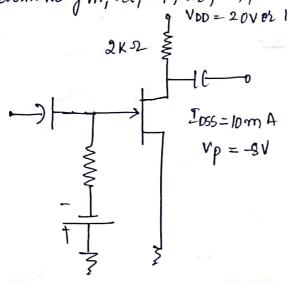

# Low forequency response of FET templifier

Capacitive element that affect the low frequency of a JFFT amplifier

Consider the input network

$$Rinigate$$

=  $\frac{V65}{|I655|}$

V615 = Voltageacross gate and Source IGS5 = Gate reverse Current

Consider

$$\frac{\text{KCG}}{\text{Rsig} + \text{Rj}} = 1$$

Similarly Consider the output licheit

$$V_0 = \frac{V_D \left( R_L / R_0 + R_L \right)}{1 + \frac{X l G_J}{R_0 + R_L}}$$

$$f_{L_{CC}} = \frac{1}{2\pi (R_1 + R_0)} c_0$$

Consider the Cht as shown below

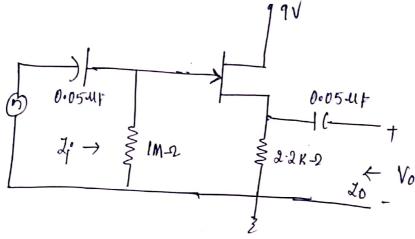

PHm: Determine the lower cutteft frequency of an FET amplifies with the following

Parameters (G = 0.01 UF, Cc = 0.5 UF, Cs = 2 UF, Rsig = 10 KD, RG = 1 MD

Parameters (G = 0.01 UF, Cc = 0.5 UF, Cs = 2 UF, Rsig = 10 KD, RG = 1 MD

RD = 4-7 KD, Rs = 1 KD, RL = 2.2 kD, ID65 = 8 mA, Vp = -47 od = 0.00, VDD = 20 V

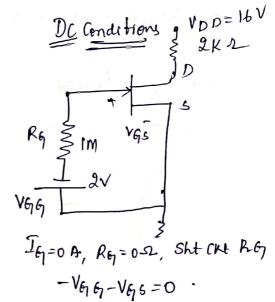

List of Dc Conditions for FE7 Amplifier.

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^{\alpha}$$

$$g_{mo} = \frac{2 \text{ Joss}}{|Vp|} = \frac{2V_{8mA}}{4V} = 4m'$$

$$g_{m} = g_{mo} \left(1 - \frac{V_{4sg}}{Vp}\right)$$

$$g_{m} = 4ms \left(1 - \frac{42V}{74V}\right)$$

$$g_{m} = 4ms \left(1 - \frac{1}{2}\right) = 2ms$$

$$g_{m} = 2ms$$

$$g_{$$

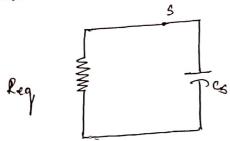

$$k_{eq} = k_{s} || \frac{1}{g_{m}} = |k_{s}|| \frac{1}{2ms} = 333.33.0$$

$$= \frac{1}{2\pi k_{eq} c_{s}} = \frac{1}{2\pi x_{333.33.0} \times 2 \times 2 \times p}$$

Midband gain of the System delermined by

$$A_{V(mi'd)} = \frac{V_0}{V_1^{\circ}} = -g_m \left( R_0 || R_1 \right)$$

$$= -2ms \left( 4.7K || 2.2K \right)$$

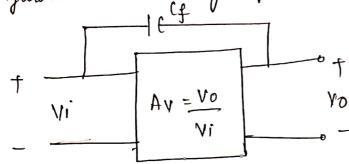

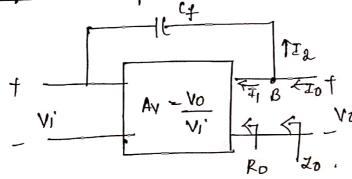

Figure shows the investing amplifier with capacitance of b/w inped & output modes.

Gain (Av) is negative for inverting amplifier Sina Vo and Vi are 180 out of phase during miller theorem we can find the loading effect of Cf on the imput and output arcuits.

→ To find miller i/p capacitome ((Mi)

$$R_{i} = \frac{V_{i}}{I_{i}} \Rightarrow I_{i} = \frac{V_{i}}{R_{i}}$$

$$Z_{i} = \frac{V_{i}}{I_{i}} \Rightarrow I_{i} = \frac{V_{i}}{Z_{i}}$$

Applying KCC at mode A.

$$J_{i} = J_{i} + J_{2}$$

$$\frac{V_{i}}{Z_{i}} = \frac{V_{i}}{R_{i}} + \frac{V_{i} - V_{0}}{X_{cf}}$$

$$\frac{V_{i}}{Z_{i}} = \frac{V_{i}}{R_{i}} + \frac{V_{i} - A_{V}V_{i}}{X_{cf}}$$

$$\frac{V_{i}}{Z_{i}} = \frac{V_{i}}{R_{i}} + V_{i} \left(1 - A_{V}\right)$$

$$\frac{V_{i}}{Z_{i}} = \frac{V_{i}}{R_{i}} + V_{i} \left(1 - A_{V}\right)$$

$$\frac{V_{i}}{Z_{i}} = \frac{V_{i}}{R_{i}} + V_{i} \left(1 - A_{V}\right)$$

$$A_{i} = \frac{A_{i}}{A_{i}}$$

$$A_{i} = \frac{A_{i}}{A_{i}}$$

$$\frac{1}{z_i} = \frac{1}{R_i} + \frac{(1-Av)}{cf}$$

$$\frac{1}{z_i} = \frac{1}{R_i} + \frac{1 - Av}{xcf}$$

$$\frac{1}{z_i} = \frac{1}{R_i} + \frac{1}{x_{c_f}}$$

$$\frac{1-Av}{1-Av}$$

[Mi - Input miller Capacitance

$$\frac{1-Av}{x_{cM_{i}} = \frac{1}{x_{cf}}}$$

Eguating Eor 2 \$ 3 we get

To find miller output Capacitance

Let

$$Y_{CM_i} = \frac{\chi_{Cf}}{1-Av} \rightarrow 0$$

$$x_{cf} = \frac{1}{2\pi f c_f}$$

$\Delta_V = \frac{V_0}{V_1}$   $\int A_V = \frac{V_0}{V_1}$

Let XCNO = Xcf

$X(f) = \frac{1}{2\pi f(f)}$

#### Applying KCL almode B.

$$I_0 = I_1 + I_2$$

$$Y_0 = Y_0 + V_0 - V_1$$

$$\frac{y_0}{z_0} = \frac{v_0}{R_0} + \frac{v_0 - v_1}{x_{cf}}$$

$$\frac{V_0}{I_0} = \frac{V_0}{R_0} + \frac{1 - V_1/V_0}{x_0 f}$$

$$\frac{1}{z_0} = \frac{1}{R_0} + \frac{1 - \frac{1}{Av}}{x_{ct}}$$

$$\frac{1}{z_0} = \frac{1}{R_0} + \frac{1}{x_0 f_{1-1/A}}$$

$$\frac{1}{Z_0} = \frac{1}{R_0} + \frac{1}{x_{CMD}}$$

which is called one miller of peopaci tomce

Conclusion! A capacitante blu i/p4 o/p nodes of an investing emplifies can be

replaced by CM: = Miller input capacitance (1-Ar) (f b) wilp & Ground

CMO= Miller output Capacitana Cf (1- 1/Av) 5/w0/p+ Broop.

If Amplifier is non-inverting replace sign by positive.

VE

At the high frequency end there are two factors that define the -3dB cutoff point the network capacitance sparasitic and wining) and frequent depending of hee (B).

Capacitive elements that affect the high frequency suspense of a JEET amplifix -

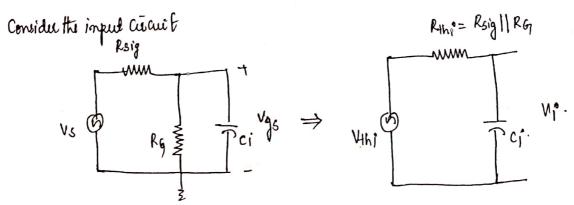

from the input liaut we have

$$V : i = \frac{V_{\text{thi}} \times ci}{R_{\text{thi}} + x_{\text{ci}}}$$

$$V : i = \frac{V_{\text{thi}} \times ci}{\frac{R_{\text{thi}} \times ci}{x_{\text{ci}}}}$$

$$\left(\frac{R_{\text{thi}}}{x_{\text{ci}}} + 1\right) \times c_{\text{ci}}$$

$$\frac{1 \cdot \sqrt{|c|}}{\sqrt{1 + \left(\frac{R_1 R_1}{|c|}\right)^2}} \Rightarrow 0$$

f=0, xq=0 and f=0, xq=0 on Substituting this Condition

Consider Rthi = 1

$$Xc_i^\circ$$

$Xc_i^\circ = Rth_i^\circ$

$f_{H_i^\circ}^\circ = \frac{1}{2\pi Rth_i^\circ C_i^\circ}$

$$C_{M_1}^{\circ} = (1 - Av) c_f$$

$$C_{M_1} = (1 - Av) c_f$$

$$Av = -gm(RD||RL)$$

$$gm = gmo(1 - \frac{V_{05}}{V_p})$$

$$gmo = \frac{2 ID55}{|V_p|}$$

$$f=\infty$$

,  $x_{c_1}=0$  f  $f=0$ ,  $x_{c_1}=\infty$  on Substitutiong im 2

we get  $|V_0|=|V_0|$  i.e  $|V_0|$  mid =  $|V_0|$  lonsides  $\frac{R_0}{x_{c_0}}=1$

$\frac{1}{2\pi R_0}$   $\frac{1}{2\pi R_0}$   $\frac{1}{2\pi R_0}$   $\frac{1}{2\pi R_0}$   $\frac{1}{2\pi R_0}$

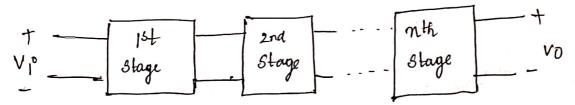

Assuming identical n-stages of amplifiers connected in Cascaded as Shownin big Let the mid band gain of Each of the Stages be Avined

Cas caded connection q on number of Rc-coupled amplifiers.

For the low frequency the overall voltage goin is given by

Since all the stage are identical.

Av, (low) = Av2 (low) = Av(3) low = Av(n) low.

The low frequency gain Avidow) for one stouge is given

$$|Av(dow)| = |Av(mid)|$$

$$\sqrt{1+(f/f)^2}$$

For m-stage in Cascade Connection we have

$$\left\{ \frac{|Av(low)|}{|Av(mid)|} \right\}^n = \frac{1}{\sqrt{2}}$$

Eq (1) becomes.

$$\frac{1}{\sqrt{2}} = \left[\frac{1}{1 + \left(\frac{f_1}{f_{L(m)}}\right)^2}\right]^n$$

$$\sqrt{2} = \left[\sqrt{1 + \left(\frac{f_1}{f_{L(m)}}\right)^2}\right]^n$$

Squaring on both the sides

taking nth root on both Side

$$2^{1/n} = \left[ 1 + \left( \frac{f}{f} \right) \right]^{2}$$

$$2^{\frac{1}{2}} = 1 + \left(\frac{f_1}{f_{L(n)}}\right)^2$$

$$g^{1/n}-1 = \left(\frac{f_1}{f_{L(n)}}\right)^2$$

$$\frac{f_1}{f_{kn}} = \sqrt{g^{ln}-1}$$

$$\exists L(m) = \frac{\exists 1}{\sqrt{2^{1/n}-1}}$$

Juin > Lower 3 d B frequency of identical coacaded stages.

### overall high frequency cult-off frequency of multistage amplifier

$$\begin{cases} \frac{1}{A \vee \text{chigh}} \\ \frac{1}{A \vee \text{cmid}} \\ \frac{1}{A \vee \text{cmid}} \\ \frac{1}{A \vee \text{cmid}} \\ \frac{1}{A \vee \text{cmid}} \\ \frac{1}{A \vee \text{chigh}} \\ \frac{1}{A \vee$$

Let  $f_{H(n)}$  be the upper frequency of the amplifies having n-stage. Then at this frequency  $f_{H(n)}$  we have.

$$\int \left| \frac{Av(high)}{|Av(mid)|} \right|^{n} = \frac{1}{\sqrt{2}} \quad \text{ equation } 0 \text{ becomes}.$$

$$\frac{1}{\sqrt{2}} = \left\{ \frac{1}{1 + \left(\frac{f_{+}(m)}{f_{2}}\right)^{2}} \right\}^{\eta}$$

$$\sqrt{2} = \left\{ \sqrt{1 + \left(\frac{f_{+}(m)}{f_{2}}\right)^{2}} \right\}^{\eta}$$

Squarings taking onth root

$$2^{1/\eta} = \left\{ 1 + \left( \frac{f + (\eta)}{f_2} \right)^{\frac{\eta}{2}} \right\}^{\eta/\eta}$$

$$\left(\frac{1}{4} + \frac{1}{4}\right)^2 = 2^{1/n} - 1$$

$$\frac{f_{H(n)}}{f_{2}} = \sqrt{g^{1/n}-1}$$

Chapter - 2 Romya Aut profusor Dept of ECE

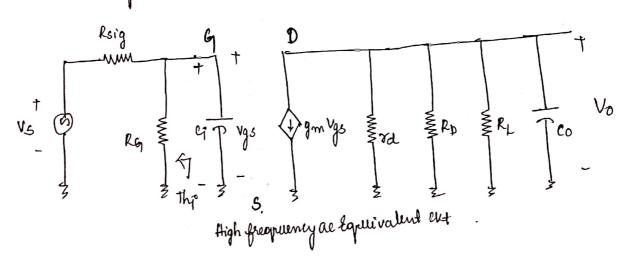

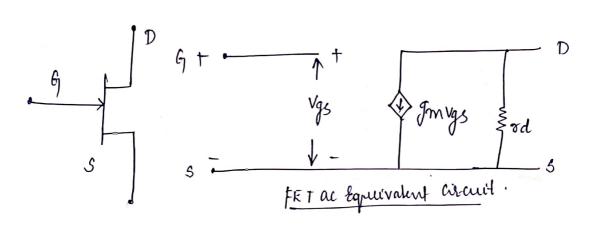

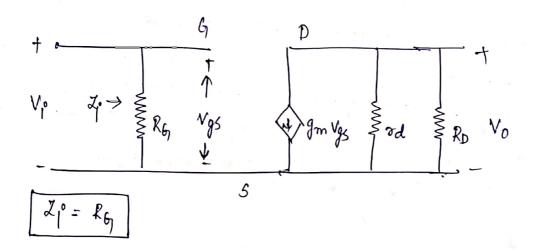

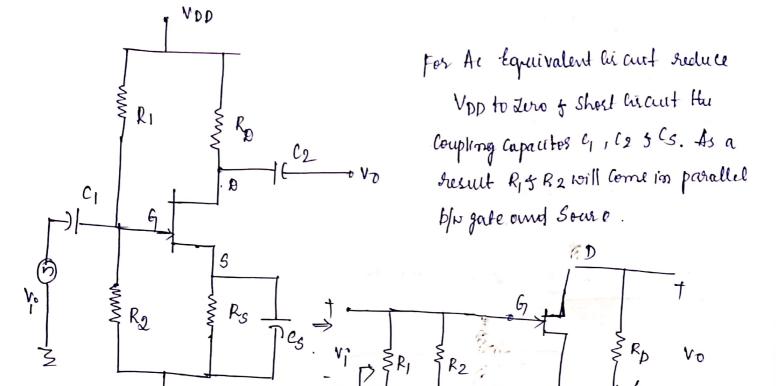

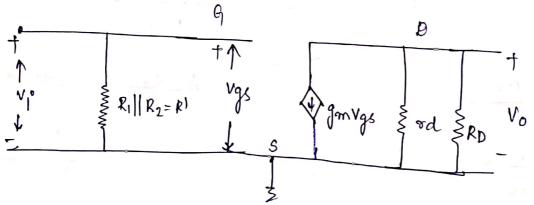

The Ac analysis of on FET Configuration requires that a small signal ac male for the FET to be developed.

An ac Voltage applied to the input gate to Source terminal will contend the terrel of current from drawn to source

Gate to Soura Voltage Controls Its drawn to soura current of an PET

The de Vgs Controls Its level of de drain Current Thorough a relationship Known, as Shockleys Equation

$$J_D = J_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

The change in gate to Soura voltage can be determined using the transconductance factor gon in the following manner

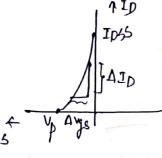

Definition of gon using transfer characters to

$$g_m = m = \underline{Ay} = \underline{AID}$$

$\underline{AZ} = \underline{AID}$

$$g_{m} = \frac{dI_{D}}{dV_{h}s} = \frac{d}{dV_{h}s} \left( I_{DSS} \left( 1 - \frac{V_{h}s}{V_{p}} \right)^{2} \right)$$

$$g_m = I_{DSS} \frac{d}{dv_{GS}} \left(1 - \frac{V_{GS}}{v_p}\right)^2$$

$$g_{m} = 2 J_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right) \left( \frac{d}{dV_{GS}} \right) - \frac{1}{V_{P}} \frac{dV_{GS}}{dV_{GS}} \right)$$

$$g_{m} = 2 J_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right) \left( 0 - \frac{1}{V_{P}} \right)$$

$$g_{m} = \frac{2 J_{DSS}}{1 V_{P}} \left( 1 - \frac{V_{GS}}{V_{P}} \right)$$

$$J_{VGS} = 0V$$

FET i/p impedance: Input impedance of out the FET's is sufficiently large to assume that the i/p terminous approximate an open account in Equation form.

It is typically practical value of 1092 = 1000M2

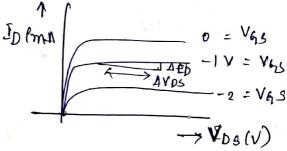

FET Ofpionfedonce: output impedance of FET'S are Zo = rd = 1/yos

Yos = 45 (units) is parameter consponent of an admittance Equivalent arount

$$\mathcal{T}d = \frac{\Delta V_{DS}}{\Delta I_D} \bigg|_{V_{SS} = \hat{\mathbf{0}}_{onstand}}$$

A model for the FET transister in the ac domain can be constructed the control of Id by Vgs is included as a current source Vgs gm Connected from drain to source.

The current source has its arrow pointing from drawn to source to establish a 180° phase shift blw output and input Voltages as will occur in actual operation.

The i/p impedance is represented by the open-circuit at the i/p terminals and the output impedance by received from drain to Source. Source is common to both input and output aracks where as gate and drown Source is common to both input and output aracks where as gate and drown ferminals are only in touch through the Controlled awrent source gm Vgs terminals are only in touch through the Controlled awrent source whose of is ignored. The topulvalent arack is simply a current source whose of is ignored. The topulvalent arack is simply a current source whose Magnetude is controlled by the signal Vgs and parameter gm.

Clearly voltage controlled devia).

#### Configurations

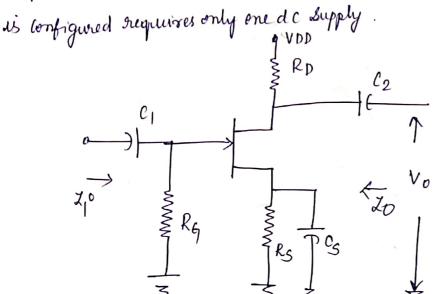

JEET fixed bias configuration

JEET Self buis Configuration

JFE7 Voltage divider bias configuration

JFIT Source follower Clommon drain) Configuration

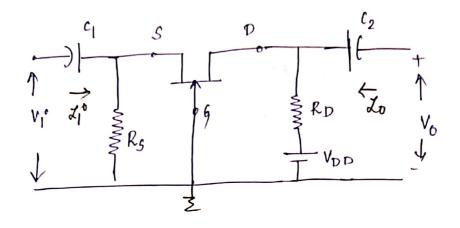

JEET common gale configuration.

Assume VGG=OV, VDD=OV.

The fixed bias

configuration the

coupling capacitors C, 3

configuration the

coupling capacitors C, 3

configurations capacitors C, 3

configurations late the de

biasing arrangement

from applied signal and

load. They act as short

circuit Equivalents for the

Ac analysis.

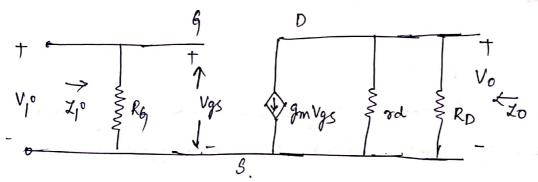

#### Ac Equivalent arcuit

The output impedance

$$Z_0 = R_D || \sigma_d$$

If the resistance rd is kufficiently large om A Food & RD & Zo Compared to ko the Approximation

$$A_{V} = \frac{V_{0}}{V_{i}^{c}}$$

$$V_{0} = -J_{0} R L$$

$$V_{0} = -g_{m} V_{gs} (\sigma d || R_{D})$$

$$V_{0} = -g_{m} V_{i}^{c} (\sigma d || R_{D})$$

$$\frac{V_{0}}{V_{i}^{c}} = -g_{m} (\sigma d || R_{D})$$

$$A_{V} = -g_{m} (\sigma d || R_{D})$$

$$\sigma d \geq 10RD$$

Av= -gm RD

Problem: For fixed bias Configuration had on operating point defined by VGSCB) = -2V & IDB = 5.625m A with IDSS = 10m A, Vp=-8V, YDS = 40US

Determine gm, od, Li, Lo, Av, determine Av by ignoring od.

$$J_{PB} = J_{PSS} \left( 1 - \frac{V_{PSS}}{V_{P}} \right)^{2}$$

$$= lomA \left( 1 - \frac{J_{SV}}{J_{V}} \right)$$

$$= lomA \left( 1 - 0.25 \right)^{2} = lomAx (0.45)^{2} = 5.625 m R$$

$$J_{m} = J_{mo} \left( 1 - \frac{V_{OS}}{V_{P}} \right)$$

$$= 2.5 ms \left( 1 - \frac{J_{SV}}{J_{S}} \right)$$

$$J_{m_{1}} = 1.88 ms$$

$$J_{Vp_{1}} = \frac{J_{SS}}{J_{Vp_{1}}} = \frac{J_{SS}}{J_{Vp_{1}}} = \frac{J_{SS}}{J_{SS}}$$

$$J_{C} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}}$$

$$J_{C} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}}$$

$$J_{C} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}} = \frac{J_{SS}}{J_{SS}}$$

$$J_{C} = \frac{J_{SS}}{J_{SS}} = \frac$$

4

fixed bias requires 2 de Sources i e disadvantage therefore suy kins

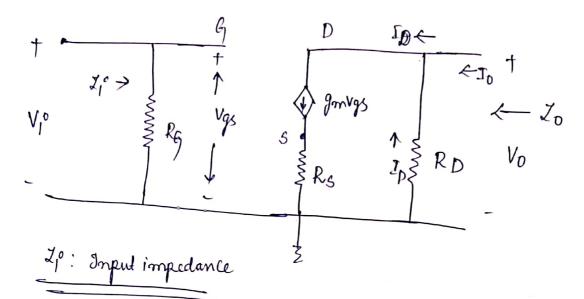

Ac Equivalent Cht: Neglect all the de Sources & C, & (2, G are 5ht-Ckted Neglect lit Effect of Rs.

Input impedance: Zo=RE

ontput impedana: Zo=RD||rd

Zo=RD||rd

Zo=RD||rd

Av: Gain:  $Av = \frac{Vo}{V_1^{\circ}}$   $V_0 = -I_0 RL = -g_m V_q s(R_0||rd)$   $V_q = V_1^{\circ} = -g_m V_1^{\circ} (R_0||rd)$   $Av = \frac{V_0}{V_1^{\circ}} = g_m (R_0||rd)$

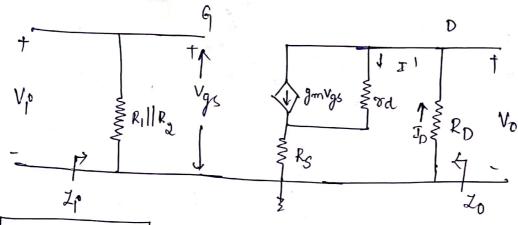

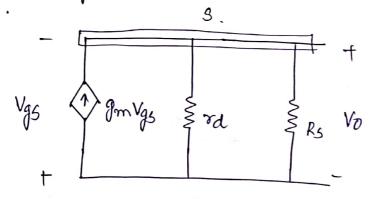

# unbypassed Rs: Considu His Effect of Rs ineglect od)

Lo: output impedance is defined by

$$Z_0 = \frac{V_0}{J_0} / V_i = 0$$

Vi=0V in the Ckt results in the gate terminal being at ground Potential. The voltage across RG is then OV & RG has been Effectively shorted out

# Apply KCL abross output loop

$$I_0 + I_D = g_m V_{gs}$$

$$V_{gs} = - (I_0 + I_D) R_g$$

$$I_0 + I_D = -g_m (I_0 + I_D) R_s$$

$$I_0 + I_D = -g_m I_0 R_s - g_m I_D R_s$$

$$I_0 + g_m I_0 R_s = -I_D - g_m I_D R_s$$

$$I_0 \left( 1 + g_m R_5 \right) = -I_D \left( 1 + g_m R_5 \right)$$

$$I_0 = -I_D$$

The Controlled Current Source

Jan Vgs = 0 A for the

applied Conditions

$$N_{0} = -I_{0}R_{D}$$

$$N_{0} = -(-I_{0})R_{D}$$

$$V_{0} = -I_{0}R_{D}$$

$$\frac{V_{0}}{I_{0}} = R_{D}$$

$$\frac{Z_{0} = R_{D}}{I_{0}}$$

$$Z_{0} = \frac{V_{0}}{I_{0}} = R_{D}$$

$$T_{0} = \frac{V_{0}}{I_{0}} = R_{D}$$

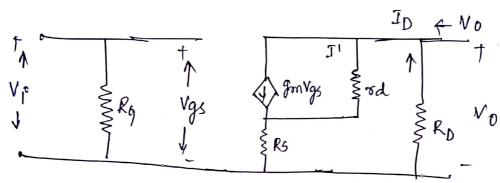

# Ay Gain for Self Rias Configuration

KVL across the che

$$V_{1}^{\circ} = V_{g_{5}} - V_{R_{5}} = 0$$

$$V_{g_{5}} = V_{1}^{\circ} - V_{R_{5}}$$

$$V_{g_{5}} = V_{1}^{\circ} - I_{D}R_{5} \rightarrow 0$$

KCL across the opploop

Consider voltage aboss rd

$$V_{rd} = V_0 - V_{RS}$$

$$I' = \frac{V_{rd}}{rd} = \frac{V_0 - V_{RS}}{rd}$$

$$I_{D} = \int m V_{g} s + \frac{V_{0} - V_{RS}}{r d}$$

$$I_{D} = \int m (V_{1}^{o} - I_{D}R_{S}) + \frac{V_{0} - V_{RS}}{r d}$$

$$I_{D} = \int m V_{1}^{o} - \int m I_{D}R_{S} + \frac{(-I_{D}R_{D}) - I_{D}R_{S}}{r d}$$

$$I_{D} = \int m V_{1}^{o} - \int m I_{D}R_{S} + \frac{I_{D}R_{D} + I_{D}R_{S}}{r d} = \int m V_{1}^{o}$$

$$I_{D} = \int m V_{1}^{o} - \int m V_{1}^{o$$

For a Sey kins configuration has an aperating point defined by Vasca) =-2.60 and IDg = 2.6mA, with IDSS = 8mA, Vp =-60, yos= 20.45 determine gm, rd, Io, Zo with a without rd, Av with our without rd.

$$\int m_0 = \frac{2 J_{D55}}{|V_p|}$$

$$\int m_0 = \frac{2 \chi_{8mA}}{\delta} = \frac{16m}{6} = 2.66m5$$

$$\int m = \int m_0 \left(1 - \frac{V_{950}}{V_p}\right)$$

$$= 2.66m5 \left(1 - \frac{-2.6V}{20.6M}\right)$$

$$\int m = 1.51m5$$

with 7d

$$A_{V} = -\frac{9m RD}{1 + 9m R_{S} + \frac{RD + RS}{7d}} = -\frac{(1.51mS)(3.8K)}{1 + 1.51mx1K + 3.3K + 1K}$$

$$A_{V} = -\frac{4.983}{1 + 1.51 + 0.086} = -\frac{4.983}{2.596}$$

$$A_{V} = -1.92$$

$$A_{V} = -g_{m}R_{D}$$

$$I + g_{m}R_{S}$$

$$A_{V} = -(1.51m_{S})(3.3k)$$

$$I + 1.51m_{S} \times IK_{D}$$

$$A_{V} = -1.98$$

Zp

Al Equivalent hi aut using small signal ac model of JFRT

$$V_0 = -I_0 RL$$

$$V_0 = -g_m V_{gs}(rd||R_D)$$

$$V_0 = -g_m V_{i}(rd||R_D)$$

$$\frac{V_0}{V_{i}^{\circ}} = -g_m (rd||R_D)$$

$$A_V = -g_m (rd||R_D)$$

## with unbypassed Rs:

$$Z_0 = \frac{V_0}{I_0}$$

$$Z_0 = \left[ 1 + g_m R_s + \frac{R_s}{rd} \right] R_D$$

$$\left[ 1 + g_m R_s + \frac{R_s}{rd} + \frac{R_D}{rd} \right]$$

Neglecting the Effect of vol

Ay = Vo Vjo = - gm RD I+gmRs + RD+Rs

Peroblem

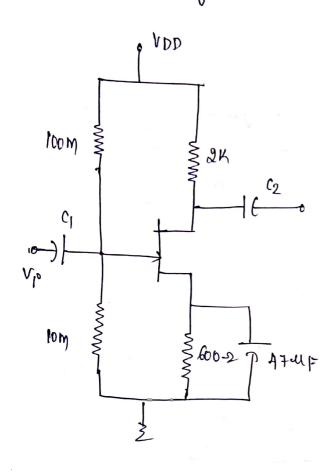

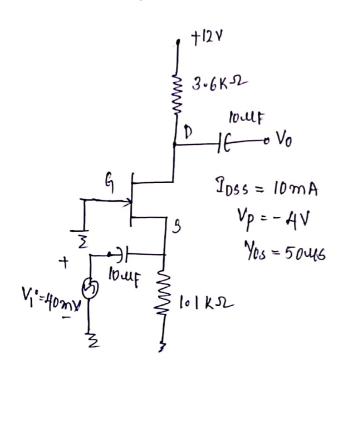

FOR JEET Voltage divider bias Calculate Z1°, Zo, Av find Voit V1°=25 mV(2008)

$$g_m = 8ms \left(1 - \frac{\pm 1}{\pm 3}\right)$$

$$g_m = 8ms \left(1 - \frac{1}{3}\right)$$

$$g_m = 5.33ms$$

$$I_{DSS} = 12mA$$

$$V_{p} = -3V$$

$$Y_{0S} = 10MS$$

$$V_{9SB} = -1V$$

$$J_{mo} = \frac{2 \text{ IDSS}}{|V_{p}|} = \frac{2 \text{ X} 12m \text{ A}}{3}$$

$$J_{mo} = 8mS$$

$$J_{mo} = 8mS$$

$$Z_{1} = R_{1} || R_{2} = 100 \text{ m} || 10m$$

$$Z_{10} = 9.09 \text{ m} \Omega$$

$$Z_0 = rd||R_D = 100 kJ2||2k$$

$Z_0 = 1.96 kJ2$

$A_V = -9m (rd||R_D)$

$A_V = 5.33m5 (100 k||2k)$

$A_V = -1044$

$$V_0 = A_V V_1^0$$

=  $(-10.44) \times 25m V$

$V_0 = -0.26 V (rank)$

$$Z_{0} = R_{1} || R_{g} = 9.09 \, \text{k-D}$$

$$Z_{0} = 2 \, \text{k-D} = R_{D}$$

$$1 + g m R_{S}$$

$$= - \left( 5.33 \, \text{m/s} \right) (2 \, \text{k})$$

$$1 + (5.33 \, \text{m/s}) (600 - 2)$$

$$A_{V} = -2.53$$

$$V_{0} = A_{V} \, V_{1}^{o}$$

$$= - (2.53) (25 \, \text{m/s})$$

$$V_{0} = - 63.25 \, \text{m/s} (7 \, \text{m/s})$$

$$Z_0 = \left[1 + g_{\text{m}} R_{\text{S}} + \frac{R_{\text{S}}}{rd}\right] R_D$$

$$\left[1 + g_{\text{m}} R_{\text{S}} + \frac{R_{\text{S}}}{rd} + \frac{R_D}{rd}\right]$$

$$Z_0 = \left[1 + 5 \cdot 33 \text{ ms} \times 600 \cdot 2 + \frac{600 \cdot 2}{100 \text{ K}}\right] 21$$

$$\left[1 + 5 \cdot 33 \text{ ms} \times 600 \cdot 2 + \frac{600 \cdot 2}{100 \text{ K}} + \frac{2 \text{ K}}{100 \text{ K}}\right]$$

$$Z_0 = 2 \text{ K} \Omega$$

9

The output is taken off the source terminal & when the de supply is replaced by its short artwit Equivalent the derain is grounded Chence the terminology Common duain)

JEET Source follower configuration

The Controlled Source and the indernal output impedance of the JFET are tied to ground at one end and Rs on the other with Vo across Rs. Since Im Vgs, rd and Rs are Connected to the Same terminal and ground they can be placed in parallel. The Current Source is in reverse direction but Vgs is still defined blue the gate and Source terminals.

To, Selling Vi=0 the resultant cut is shown below.

Vgs & Vo are across the same parallel n/w results in

Apply KCL across node 5

$$I_{0}+g_{m}V_{gs}=I_{rd}+I_{RS}$$

$$I_{0}+g_{m}V_{gs}=\frac{V_{0}}{v_{d}}+\frac{V_{0}}{R_{s}}$$

$$I_{0}=V_{0}\left[\frac{1}{r_{d}}+\frac{1}{R_{s}}\right]-g_{m}V_{gs}$$

$$I_{0}=V_{0}\left[\frac{1}{r_{d}}+\frac{1}{R_{s}}\right]-g_{m}\left(-V_{0}\right)$$

$$I_{0}=V_{0}\left[\frac{1}{r_{d}}+\frac{1}{R_{s}}+g_{m}\right]$$

Apply Kirchoffs Voltage law around the perimeter of the m/D

$$V_{i}^{o} = V_{gs} + V_{0}$$

$$V_{gs} = V_{i}^{o} - V_{0} \rightarrow \emptyset$$

Substitute 1 in 1

$$A_V = \frac{V_0}{V_1^0} = \frac{g_m(rd||R_S)}{1 + g_m(rd||R_S)}$$

Pasitive Sign for Av reveals that Vogv; are in phase.

\*\*

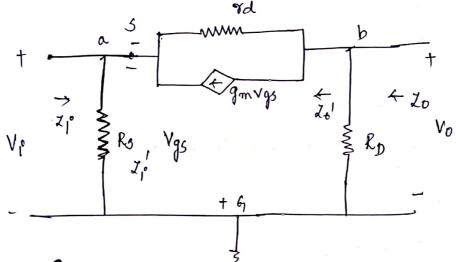

Consider the Circuit as Shown kelow.

tiga Ac Equivalent Circuit Ming JEET Small seignal Model.

Controlled Current Source g m Vgs be connected from drain to Lour e with od m parallel. The isolation b/w i/p and o/p cis cuit has been lost since the gode terminal is Common ground of the network

where 2, is the impedant booking into Sour would gote terminals building Rs.

To find di the n/w is redraum as shown below.

The voltage V=-Vgs Apply kv L accound the perimeter of the Mp results in

$$V' - V_{rd} - V_{RD} = 0$$

$$V_{rd} = V' - V_{RD}$$

$$V_{rd} = V' - J' R_{D} \rightarrow 0$$

Apply KC L alross node a

$$I' + g_m Vgs = I_{rd}$$

$$I_{rd} = (V' - J' R_D)$$

I'= Ird-9m Vgs Substituting Ird in the above Equation we get.

$$I' = \frac{(V' - I'RD)}{rd} - g_m V_{gs}$$

$$I' = \frac{V'}{rd} - \frac{I'RD}{rd} - g_m (V')$$

$$J' + \frac{I'RD}{rd} = \frac{V'}{rd} + \frac{gmV'}{rd}$$

$$I'\left(1+\frac{RD}{rd}\right) = V'\left(\frac{1}{rd} + gm\right)$$

$$J_{i}^{\prime} = \frac{V^{\prime}}{I^{\prime}} = \frac{rd + RD}{rdV} = \frac{rd + RD}{1 + gmrd}$$

$$Z_{i}^{\prime} = R_{s} || \frac{rd + RD}{1 + gmrd}$$

$$J_{1}^{1} = \frac{\left[1 + \frac{RD}{rd}\right]}{\left[\int_{a}^{b} m + \frac{1}{rd}\right]}$$

Shorted out and Set ys =0 v : gmvgs =0 od will be in parallel with Rp.

$$I_0 = R_D$$

$$\frac{\text{Gain}}{\text{Vi}^{\circ}} : A_{V} = \frac{V_{0}}{V_{i}^{\circ}}$$

Voltage alress od is Vod = Vo-Vio

$$I_{rd} = \frac{V_0 - V_1^0}{\pi d}$$

Apply KCL across node 6 in the fig @ we get

$$I_{rd} + I_{D} + g_{m} \vee g_{s} = 0$$

$$I_{D} = -I_{rd} - g_{m} \vee g_{s}$$

$$= - \left[ \frac{v_{0} - v_{i}^{\circ}}{2} \right] - g_{m} \left( - v_{i}^{\circ} \right)$$

$$J_{D} = \frac{V_{1}^{o} - V_{0}}{\tau d} + g_{m}V_{1}^{o}$$

$$V_{0} = J_{D}R_{D} = \left[ \frac{V_{1}^{o} - V_{0}}{\tau d} + g_{m}V_{1}^{o} \right]R_{D}$$

$$= \frac{V_{1}^{o}R_{D}}{\tau d} - \frac{V_{0}R_{D}}{\tau d} + g_{m}V_{1}^{o}R_{D}$$

$$V_{0} = \frac{V_{1}^{o}R_{D}}{\tau d} - \frac{V_{0}R_{D}}{\tau d} + g_{m}V_{1}^{o}R_{D}$$

$$V_{0} + \frac{V_{0}R_{D}}{\tau d} = \frac{V_{1}^{o}R_{D}}{\tau d} + g_{m}V_{1}^{o}R_{D}$$

$$V_{0} \left[ 1 + \frac{R_{D}}{\tau d} \right] = V_{1}^{o} \left[ \frac{R_{D}}{\tau d} + g_{m}R_{D} \right]$$

$$V_{0} = \frac{g_{m}R_{D} + \frac{R_{D}}{\tau d}}{\tau d}$$

$$A_{V} = \frac{V_{0}}{V_{1}^{c}} - \frac{g_{m}R_{D} + \frac{R_{D}}{\tau d}}{\left[1 + \frac{R_{D}}{\tau d}\right]}$$

for rd>10RD, the factor Roped lanks nighted as a good approximation of  $AV = g_{m}R_{D}$   $V = g_{m}R_{D}$

phase relationship: ty is the will result in an imphase relationship b/w V05 V1° for common gate Configuration.

## Broblem on Common Soura Amplifier

For a Source follower networks results in Vgsg = -2.86 V & IDg = 4.56m

Determine gom, od, Zif also calculate Lo with 5 without od, Av with our without od.

$$g_{mo} = \frac{2 \text{ IDSS}}{|Vp|} = \frac{2 \times 16 \text{m } \Delta}{4 \text{ y}} = 8 \text{ms}$$

$$gm = gm_0 \left(1 - \frac{V_{95}}{V_p}\right)$$

=  $8m \left(1 - \frac{+2.86}{-4}\right)$

$gm = 2.28m_5$

$$Z_0 = R_5 | 1 / g_m$$

$Z_0 = 2.2 K | 1 / 2.28 ms$

$Z_0 = 365.6952$

$$A_{V} = \frac{4.77}{1+4.77} = 0.83$$

Problem on Common gate Configuration

For the figure schown below is a Common gate Configuration with  $V_{GS} = -3.2V$ and  $I_{DS} = 2.03 \, \text{mA}$ , Determine  $g_{m}$ , od Calculate  $I_{I}^{o}$  with \$100 thank od \$1.20 ditermine Vo 101 th and with out od.

$$g_{mo} = \frac{2J_{DSS}}{|V_p|}$$

$$g_{mo} = \frac{2 \times 10 \text{ mA}}{4 \text{ V}} = 5 \text{ ms}$$

$$g_{mo} = 5 \text{ ms}$$

$$g_{mo} = g_{mo} \left(1 - \frac{V_{GS}}{V_p}\right)$$

$$= 5 \text{ ms} \left(1 - \frac{42.2 \text{ V}}{+4}\right)$$

$$= 5 \text{ ms} \left(1 - \frac{2.2}{4}\right)$$

$$g_{mo} = 2.25 \text{ ms}$$

with out od.

Northented

$$Z_0 = 3.6 \, \text{K} \parallel 20 \, \text{K} \cdot 20 \, \text{K}$$

$$A_V = (2.25m)(3.6k) + (3.6K/20K)$$

$$1+ (3.6K) + (3.6K/20K)$$

$$AV = \frac{8.1 + 0.18}{1 + 0.18} = 7.02$$

$$A_{V} = \frac{V_0}{V_1^0}$$

$$V_0 = A_V V_1^o = (8.1) \times 40 \text{ mV}$$

$$V_0 = 324 \text{ mV}$$

Longark Assistant professer BBBIT, Dept of ECE

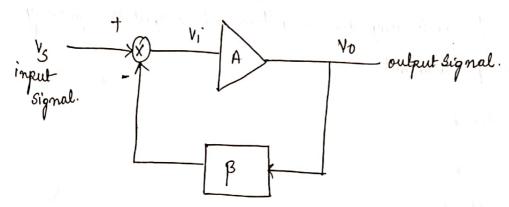

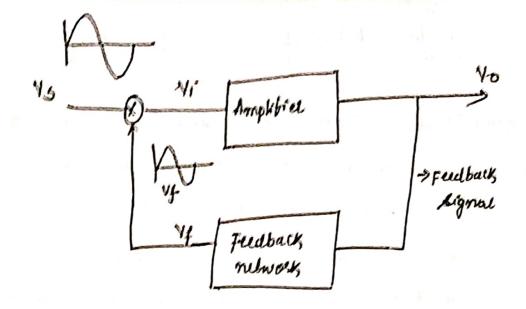

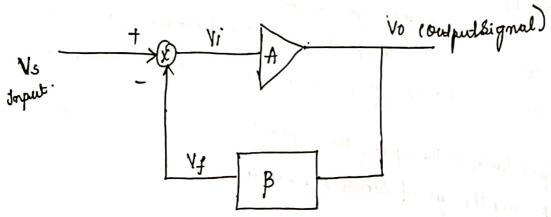

feedback: feedback us a process of Supplying a part of the output back to the input. In transistor amplifier a fraction of the output vollage may fedback to the input terminals.

Two types of feedback:

- 1) positive fudbock:

- @ Negative feedback.

Positive feedback: Both input and output are in Same phase.

Negotive feedback : Both input and output are in outphase.

Positive feedback increases the gavn of an amplifier but it increases distortion

and goin instability.

Negative fuelback decreases the gain but it reduces distortion and noise lend

The negative feedback have following advantages

- 1 Higher input Impedance

- 2 Better stabilized voltage gain

- Improved frequency response.

- Lower output Impedance

- Reduced moise and More linear operation.

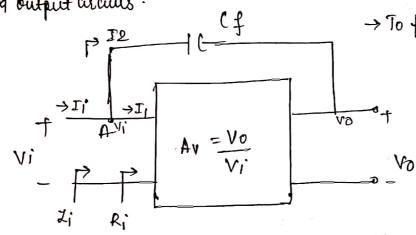

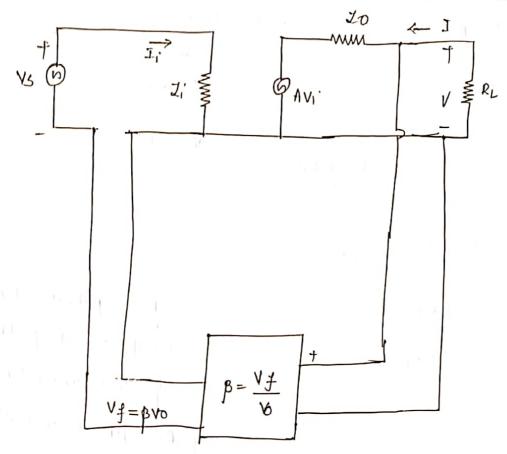

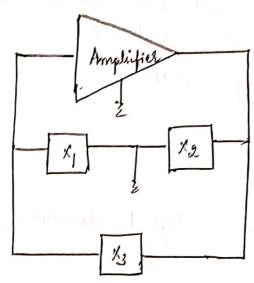

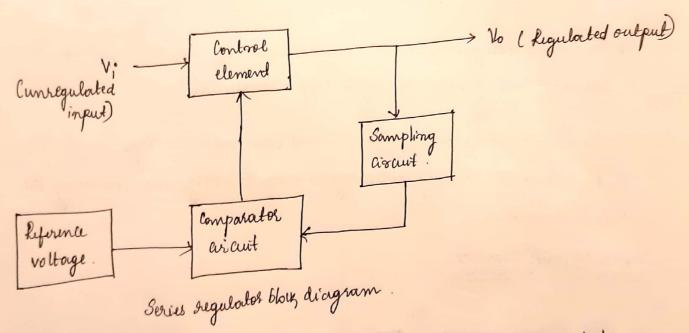

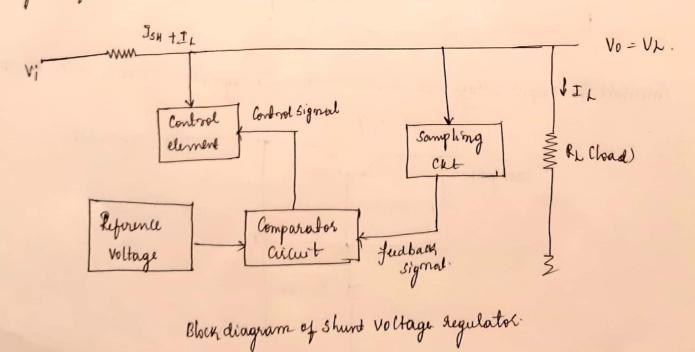

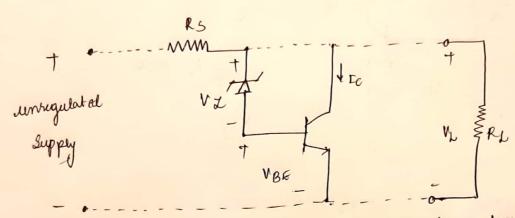

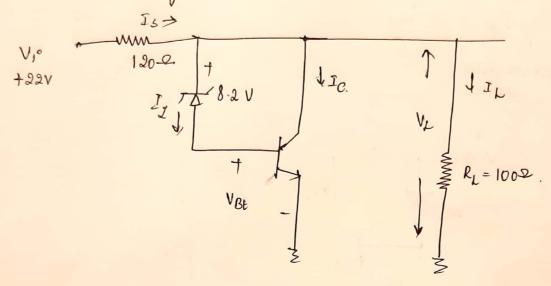

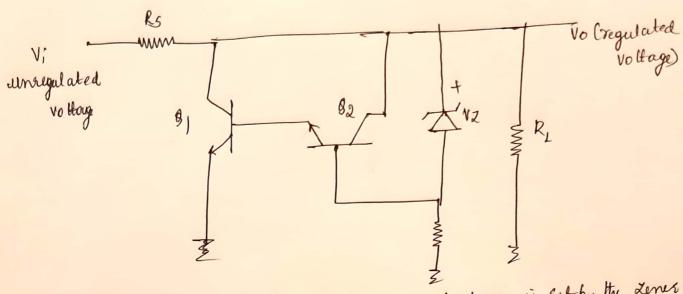

The feedback Connection is as Shown below the input signal Vs is applied to a Mixer network where it is combined with a fudback signal vf. The difference of These Signals vi is the imput voltage to the amplifier.

A portion of the amplifier output to is connected to the feed back network CB) which provides a reduced portion of the output as feedborek signal to the input mixes network

Block diagram of feedback amplefier.

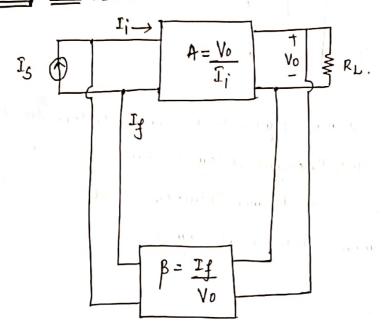

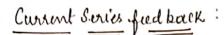

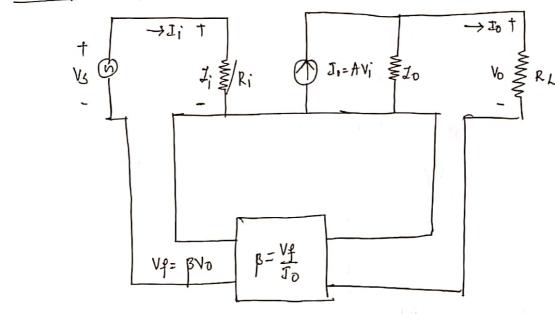

Feedback Connection types: There are four basic ways of Connecting the feedback Signal. Both valltage and Current Can be fedback to the input either in Series or parallel.

- O voltage Series feed back

- 3 Yoltage Shunt fredback

- 3 Current Peries fred back

- (4) Current Shunt feed back.

Voltage refers to Connecting the output Voltage as imput its the feed back network.

Current refers to tapping of Some output award Through the feed back network.

Series refers to Connecting the feed back signal in Series with the imput signal voltage. Shunt refers to Connecting the feed back signal in Shunt C parallel with an input award source.

Series feedback Connections are used to increase the input resistance and Shuntfeedback Connection are used to decrease the input resistance.

Voltage feed back decreases the output impedance where as aurent increases the output impedance

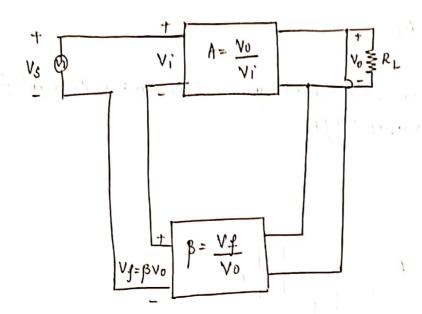

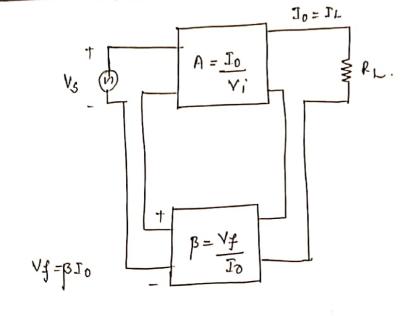

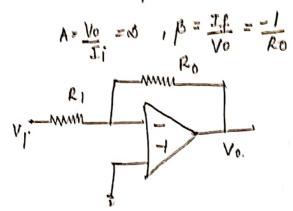

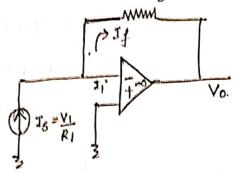

Voltage Series feedback gain with feedback: figure above shows the Voltage Series feedback Connection with a part of the output voltage feed back in Series with the input signal resulting in an onerall gain reduction. If there is no feedback cvy =0) the voltage gain of the amplifier stage is

$$A = \frac{V_0}{V_S} = \frac{V_0}{V_i} \longrightarrow 0$$

If a feedback signal Vy is connected in Socies with input then

From Equaction 1

$$A_{\frac{1}{2}} = \frac{V_0}{V_5} = \frac{A}{1 + A \cdot \beta}$$

The above Equiation shows that the gain with feedback is the amplified gain reduced by the factor of (1+ BA).

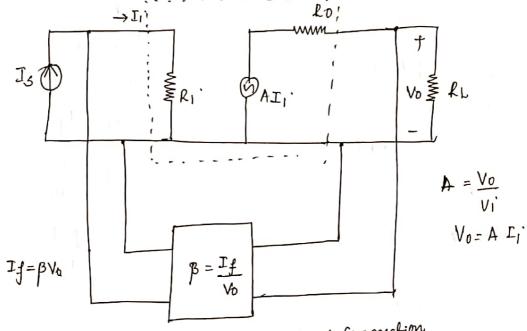

#### Voltage Shunt fudback!

The gourn of the feedback for the network is

$$A_f = \frac{V_0}{I_S}$$

$$A_{j} = \frac{A I_{i}}{I_{i} + I_{f}}$$

$$A_{j} = \frac{A I_{i}}{I_{i} + \beta V_{0}}$$

$$A_{j} = \frac{A I_{i}}{I_{i} + \beta A I_{i}} = \frac{A I_{f}}{I_{i} (1 + \beta A)}$$

$$A_{l} = \frac{A}{A}$$

$$A_f = \frac{J_0}{V_S}$$

$$A_f = \frac{T_0}{V_1 + V_f}$$

$$A_{j} = \frac{I_{0}}{V_{i} + \beta I_{0}} = \frac{AV_{i}}{V_{i} + \beta AV_{i}} = \frac{AV_{i}}{V_{i} (1 + A\beta)} = \frac{A}{1 + A\beta}$$

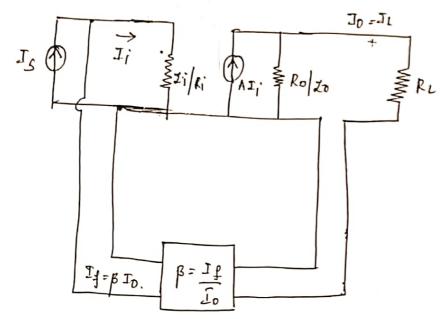

Eurrent Shunt feidback:  $I_0 = I_L$   $I_0 = I_L$

$$Af = \frac{T_0}{T_S}$$

$$Af = \frac{T_0}{T_i + T_f}$$

$$Af = \frac{T_0}{T_i + \beta T_0}$$

$$Af = \frac{T_0}{T_i + \beta A T_i}$$

$$Af = \frac{A T_i}{f + \beta A} = \frac{A}{1 + A\beta}$$

$$Af = \frac{A}{1 + A\beta}$$

Input Impedance and output Impedance with feed back

٧o

The imput Impedience can be eletermined as follous.

$$J_i' = \frac{V_i'}{Z_i'} = \frac{V_3 - V_f}{J_f}$$

$$\mathcal{I}_{i,j} = \frac{V_{i,j}}{I_{i,j}} = \mathcal{I}_{i,j}(1+\beta N)$$

Lif-I/p Impedance without feedback

Lif-I/p Impedance with feedback

Lo = output Impedance with out feedback

Loj = O/p Impedance with feedback.

The input Impulance with Series feelback is seen to be the value of the input Impudome with put feedback multiplied by itte factor (1+13A) and applies for both voltage and current series.

## output impedance with feedback.

For Vollage freed beach the output impedance is decreased the output impedance its determined by applying a voltage v resulting in a Current I will its is shorted out.

$$V = IZ_0 + AV_1$$

$$V = IZ_0 + A(-V_f)$$

$$V = IZ_0 - AY_f$$

$$V = IZ_0 - ABV$$

$$V + ABV = IZ_0$$

$$V(1+AB) = IZ_0$$

$$V(1+AB) = IZ_0$$

$$Iof = \frac{V}{I} = \frac{Z_0}{1+AB}$$

$$Iof = \frac{Z_0}{1+AB}$$

FOR

$$V_S = 0$$

$$V_1 = V_S - V_f$$

$$V_1 = 0 - V_f$$

$$V_1 = -V_f$$

$$V_2 = \beta V_0$$

$$V_3 = \beta V$$

Voltage Shunt feedback: Input Impedance and output Impedance

The i/p Impedance com ke determined to ke.

Voltage shund feedback Connection.

Input Impedance with feedback  $Zif = \frac{V_i}{I_S}$

$$I_{S} = I_{i} + I_{f}$$

$$I_{i} = \frac{V_{i}}{I_{i} + I_{f}} = \frac{V_{i}}{I_{i} + \beta V_{0}}$$

Divide Numerator and denominator by Ii

$$Zif = \frac{Vi/Ii}{Ii/Ii+\beta} VO/Ii$$

$Z_1 = \frac{V_1}{I_1}$

The Voltage Shunt feedborck amplifier the imput impedance gets reduced by the factor (1+AB)

output Impedance: The ofp Impedance is determined by applying V resulting in a current J with  $V_S=0$ . I  $J_S=0$

$$V = JZ_0 + AIi$$

$$V = JZ_0 - AIi$$

$$V = JZ_0 - A\beta V$$

$$V = JZ_0 - A\beta V$$

$$V + A\beta V = JZ_0$$

$$V(I + A\beta) = JZ_0$$

$$V(I + A\beta) = JZ_0$$

$$\frac{V}{J} = \frac{Z_0}{I + A\beta}$$

$$Z_0 f = \frac{V}{I} = \frac{Z_0}{I + A\beta}$$

DAT

$$I_S = I_1 + I_f$$

$$I_S = 0$$

$$I_1 = -I_f$$

$$\beta = \frac{I_f}{V_0}$$

$$I_f = \beta V_0$$

$$I_f = \beta V$$

Input Impedance of Current Series fudballs

$$J_{1} = \frac{V_{1}}{I_{1}}$$

$$V_{1} = V_{2} - V_{2}$$

$$V_{1} = V_{3} - V_{2}$$

$$V_{1} = V_{3} - V_{2}$$

$$V_{2} = \beta I_{0}$$

$$J_{i} = \frac{V_{s} - V_{f}}{S_{i}}$$

$$J_{i} I_{i} = V_{s} - V_{f}$$

$$J_{i} I_{i} = V_{s} - \beta S_{o}$$

$$J_{i} I_{i} = V_{s} - \beta A V_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i} I_{i}$$

$$J_{i} I_{i} = V_{s} - \beta A J_{i}$$

$$J_{i} I_{i} = V_{s} - \beta$$

output Impedance:

$$V_S = D$$

$V_S = V_i - V_f$

$V_i = V_f$

Let a voltage  $V$  be applied to the  $V_i = V_f$

Let a voltage  $V$  be applied to the greenthing current

output port and I denote the resulting current.  $I = \frac{V}{Zo} - AV_1^* \quad \text{By applying Kel at the old doop}$

$$I = \frac{V}{I_0} - AVf$$

$$I = \frac{V}{Z_0} - ABI$$

$$I + ABI = \frac{V}{Z_0}$$

$$Z_0 f = \frac{V}{I} = Z_0 (1 + Ap)$$

### Current Shunt feed back

Exput Impedance and output impedance:

$$Z_{ij} = \frac{V_{i}'}{I_{5}} = \frac{V_{i}'}{I_{5}'+I_{5}'} = \frac{V_{i}'/I_{i}'}{I_{i}'+\beta I_{5}'/I_{i}'}$$

Consider the output : account of Current Shunt feed back

$$J = \frac{70}{\Lambda} - VII$$

$$\bar{I} = \frac{V}{Z_0} - A\beta I$$

$$\frac{V}{I} = Z_0(I + A_B)$$

$\Rightarrow$  Determine the Voltage gavn, input- and output impedance with feedback for Voltage Sourd feedback having A = -100,  $R_i = 10 \, \text{k/2}$ ,  $R_0 = 30 \, \text{k/2}$  for feedback of  $\beta = -0.15$   $\beta = -0.5$ .

$$A_{f} = \frac{A}{1 + A \cdot B} = \frac{-100}{1 + (-0.1)(-100)} = \frac{-100}{11} = -9.09$$

$$20f = \frac{20}{1+A\beta} = \frac{20\times10^{3}}{1+6/00)(-0.1)} = 1.82\times52$$

$$\beta = \frac{-0.5}{4\beta} = \frac{A}{1+A\beta} = \frac{-100}{1+(-0.5)(-100)} = \frac{-100}{51} = -1.96$$

$$Zif = Zi(1+A\beta) = 10K D(5i) = 510K D$$

$$Lof = \frac{20}{1+AB} = \frac{20 \times 10^3}{51} = 392.16.2$$

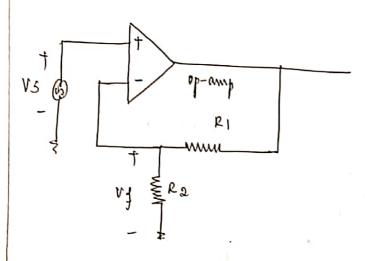

Practical feedback arcuite: Voltage Series feedback

Figure kelow shows an FET amplifier storge with voltage series feedbacks.

A part of the ofp signal Vo is obtained using a feedback, network of resistors R, and R&

The feedback voltage vy is connected in Series with the Source signal vs their difference being The input signal vi

Without feedback the amplifier going

$$A = \frac{V_0}{V_i} = -g_m R_L \rightarrow \mathbb{O}$$

For AC anodysis Consider VDD=0

Rp is analysed wort to ground Considu that has load resistance

$$R_L = R_D Ro (R_1 + R_2) \rightarrow 2$$

The feedback network provides a feedback factor of B

$$\beta \Rightarrow Vo = -V f R_2$$

$$\frac{Vo}{R_1 + R_2}$$

$$\frac{Vo}{V f} = \frac{R_2}{R_1 + R_2}$$

$$\beta = -\frac{R_2}{R_1 + R_2}$$

$$4g = \frac{-g_m R_L}{1 + \left(-\frac{R_R}{R_1 + R_2}\right) \left(-g_m R_L\right)}$$

$$\frac{A_{3} = -g_{m}R_{L}}{1 + g_{m}R_{2}R_{L}} = -g_{m}R_{L}(R_{1} + R_{2})$$

$$= -g_{m}R_{L}(R_$$

Ay =

$$-\frac{g_{m}R_{L}(R_{1}+R_{2})}{\left(\frac{(R_{1}+R_{2})}{g_{m}R_{L}}+R_{2}\right)-g_{m}R_{L}}$$

$$A_{j} = -\left(\frac{R_{1} + R_{2}}{q_{m}R_{L}} + R_{2}\right)$$

$$Ay = -(R_1 + R_2)$$

$$R_2$$

Below figure shows the voltage series fudback Connection using op-amp. The gavin of the op-amp & without fudback is reduced by the fudback factor

$$\beta = \frac{R_2}{R_1 + R_2}$$

Consider the Prester follower as Shown below provider voltage buck feel all

$$A = \frac{h_{f}e \, k_{F}}{h_{i}e}$$

$$B = \frac{V_{f}}{V_{0}} = 1$$

WET he

$$\frac{1}{1+h} = \frac{h \text{fels/hie}}{1 + h \text{fels/hie}}$$

hie + hjer hie

The elphone voltage is the larger voltage. The opposite voltage in course with the larger voltage. The completes of huma have possible its equation of the bescurt without althour the course on of the bescurt without fuellaw, possible of althour fuellaw.

Charmet States food fact I in this feed back becominged the Sample output account to and schom a proportional voltage in Source with the imput. The Current States feed back committee increases impact susustance.

Consider the figure as Shown below Single Stage Counselor amplifier Since the finites of this stage has an embyroused bracker it Effectively how Coursel Series feedback.

The turnent through desistor by sessetts in a feedback voltage that opposes the Source signal applied so that ofp to its seedered.

Value of Ib

without feedback: NAT  $A = \frac{I_0}{V_i} = \frac{-I_b h_f e}{I_b h_i e + RE}$

$$A = -\frac{hfe}{hiefRE}$$

$$\beta = \frac{\sqrt{4}}{T_0} = -\frac{T_0}{T_0} R_E = -\frac{R_E}{T_0}$$

The input and output im pedances are Supertively

$$A = -hfe$$

$$(hie+RE)+hfeRE$$

$$A = \frac{-hfe}{hie + hfeRE}$$

The input and output Impedance are calculated as specified kelow

THE HELLERY ) = prette

The wiltage gain by with feedback

Voltage struct fred brek. The Constant gam op-ourse creat provide a voltage shart fredback for an opening ideal characterstres I'= 0, V'-0 and voltage gain of infinity

Constant gouin lieur

Equivalent accust .

The garm with feedback as then

$$Af = \frac{V_0}{I_0} = \frac{V_0}{I_1} = \frac{A}{1 + AB} = \frac{1}{B} = -\frac{R_0}{B}$$

Avy =

$$\frac{V_0}{J_S} \times \frac{J_S}{V_1} = -R_0 \left( \frac{1}{R_1} \right) = -\frac{R_0}{R_1}$$

using the FET amplifies in vy shunt feedback vf =0

The feedback is

$$\beta = \frac{Jf}{V_0} = -\frac{1}{R_F}$$

$$Af = \frac{V_0}{J_S} = \frac{A}{1+AB} = \frac{-9mRDRS}{1+(-1/RF)(-9mRDRS)}$$

The voltage gain of the Circuit with feedback is then

$$Av_f = \frac{Vo}{I_6} \times \frac{I_5}{V_5} = \frac{-9 m RDRSR_F}{R_F + 9 m RDRS} \left(\frac{1}{R_5}\right)$$

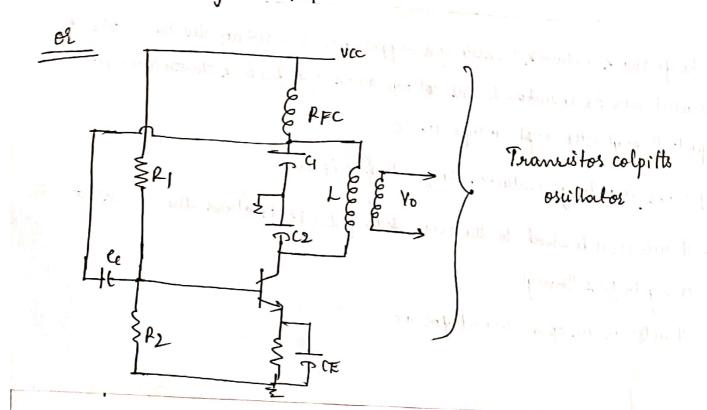

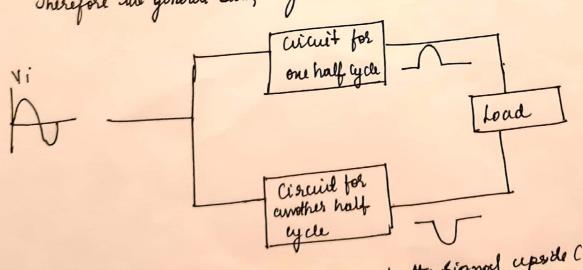

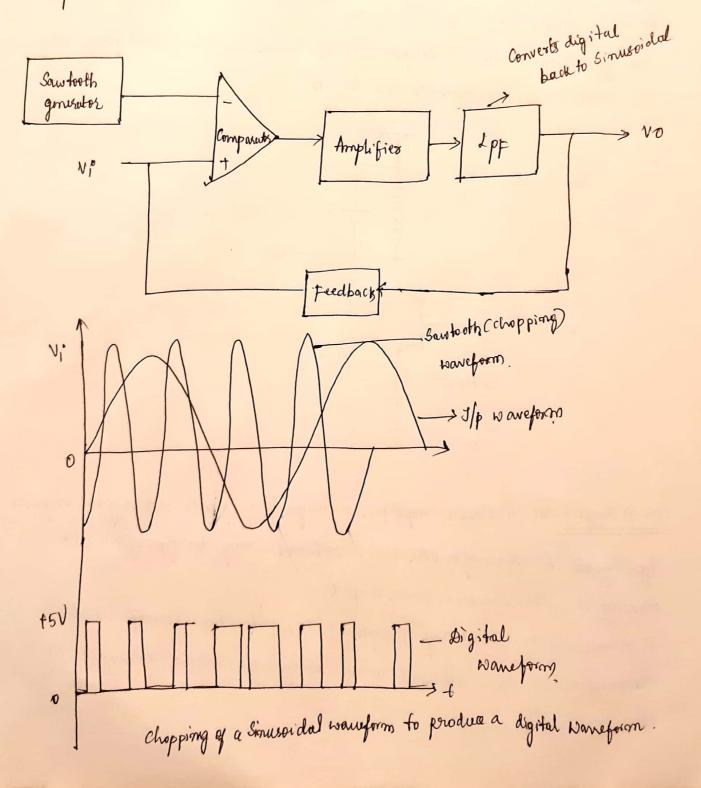

oscillators are Employed to peroduce disnusoribal digenals that are used as Carrier of Radio and Leliusion broad casts. Oscillators are also used to produce the Sequere wave used as clocks in Computer and other Synchronous Systems.

escillates is a denire which generates the Linusopetal escillations without only taternal imput. To generate the escillations it requires an amplifies ourda feed back relevous of the feedback is of positive feed back

Feedback: The perocess of injecting a fraction of output back to the input is known as feed back.

Positive fueback: when the feed back signal is in phase with the imput signal it is called as positive fuebook of amplifier is called feed back amplifier.

Negative feedback: when the feedback signal is out of phase with the input signal it is called negative feedback

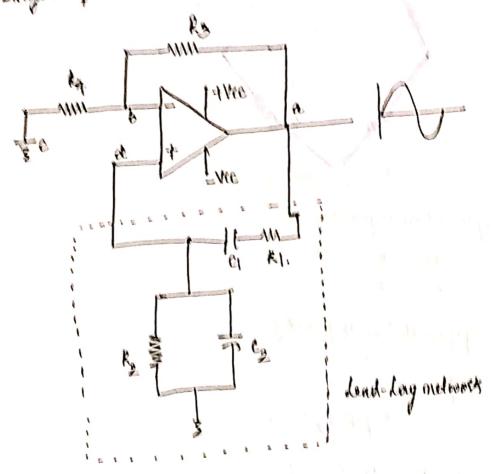

Concept of positive feedback Consider the non-investing amplified with the Voltage good A. Since the complifies is non-investing the output Voltage Vois in phase with the ifp Vs (o'phase white) the part of the output is feedback to the input with the help of a feedback network how much part of the output is to be feedback will be decided by the feedback network gain B.

The amplifier garn AV, is

$$A_{V} = \frac{V_{0}}{V_{1}}$$

This is called open loop gam of the amplifier.

The Amplifier gain A is given by

The gain of the amplifier with feedback is given by

$$h_f = \frac{V_0}{V_5}$$

This is called the closed loop gain of the amplifier.

Favor the figure WAT the fredback is possitive the voltage of its added to Yoto generate ([p of amplifier Vi

The fredback now gold as

$$\beta = \frac{y_f}{Vo}$$

Therefore Vi= Yst Yg

Consider the basic investing amplifies with on open loop gam A the feedback network attenuation factor B is less than unity. Is basic amplifies is investing it produces a phase shift of 1800 b/w input and output.

For an oscillator the feedback must be positive i.e Voltage by must be in phase with Vi Thus the feed back network must Introduce phase shift of 180°. This Ensures the positive feedback.

Basic Block dragram of oscillator Ciait

Let Vi be the Input voltage at the amplifier i/p then  $V_0 = A V_i$  ( ...  $A = \frac{V_0}{V_i}$ ) is the output voltage of the amplifier.

If

$$y_f = \beta V_0$$

(  $\beta = \frac{V_f}{V_0}$ )

The feed back voltage.

Ag is refused to as the loop goin.

$$\beta = \frac{\sqrt{4}}{\sqrt{0}} \Rightarrow \sqrt{4} = \beta \sqrt{4}$$

$$\Rightarrow \sqrt{4} = \beta \sqrt{4} \Rightarrow \sqrt{4} = \beta \sqrt{4}$$

$$\Rightarrow \sqrt{4} = \beta \sqrt{4} \Rightarrow \sqrt{4} = \beta \sqrt{4}$$

For an oscillator the feelshark network drives the amplifies we Vfacts as Vi Lo Vf = Vi

$$V_{3} = V_{i} \left(1 - A_{\beta}\right)$$

$$A_{j} = \frac{V_{0}}{V_{3}} = \frac{V_{0}}{V_{i} \left(1 - A_{\beta}\right)}$$

$$W_{i} = A_{j}$$

$$A_{j} = \frac{A_{i}}{1 - A_{\beta}}$$

$$W_{i} = A_{j}$$

New lons ides the various values of B and the lossesponding values of Az for Constant amplified gain of A of 20 A=20

| Ð  | β      | Aj      |

|----|--------|---------|

| 20 | 0.005  | 22 - 22 |

| 20 | 0.004  | 100     |

| 20 | 0.0045 | 200     |

| 20 | 0.05   | Ø       |

Conclusion: From to table it is shows that the gain with feedback increases as the amount of positive feedback increases & gain becomes infinite. This indicates that Circuit can produce output without External 1/p 45=0 i.e Ag = Yo = 0 means Yor Just by feeling the

Purt of the output back to the imput of the amplifies aircind. In this condition the circuit stops amplifying and stouts oscillating.

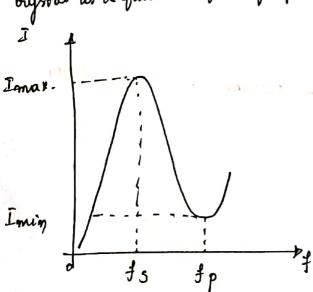

## Barkhausen Giterion

Barkhousen Oriferion States Strat

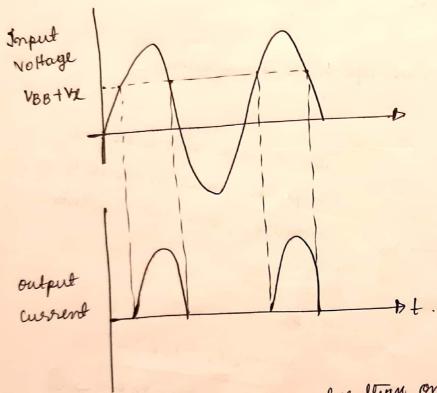

- 1 The to tal phase shift around a loop as the signal proceeds from i/p Through amplifies the feedback network back to the organ completing a coop is 0002 360° ( For inverting amplifier total phase shift around a cloge isset of for mon-inverting amplified to talphase around a doop is o')

- 2) The magnitude of the paroduct of the open loop gain of the amplified (A) & the magnitude q the feed back factor & is unity is doop gain |Ap| =1

Phase sheft around a loop is 360°. This ensure positive feedback. The two Conditions are refused as Brakhausen ordered for oscillator.

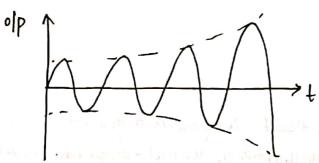

1AB > 1 the total phase sligt around a loop is 0° of 360° then the output oscillates but the oscillations are of growing type

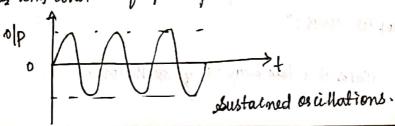

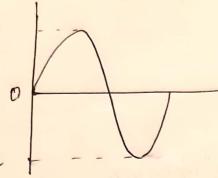

Growing type of osullations.

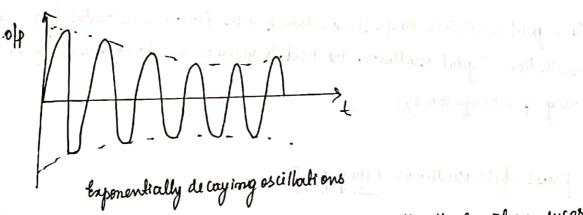

Ap/LI & when the dotal phase shift around a loop is 8 08.360 then the oscillations are decaying type 1.0 amplifude decreases be ponentially s the oscillations are finally cease

[AB=1] when the total phase around a doop is 0°05 360° than the Circuit peroduces oscillations with Constant frequency and amplifude could sustained oscillations

Note: For-the sposses ve feedback the feed back signed schooled be in phase with the imput signal.

#### classification of oscillations

Based on the clements weed in fred back, network oscillators are classified as

- 1 Rc oscillator

- 3 Lc oscillator

- 3 Crystal oscillator

- In Reoscillodors the feedback network uses Re components to generate excelledions Re oscillators are used to generate oscillations in ituaudio frequency rounge (50 Hz -20 KHz).

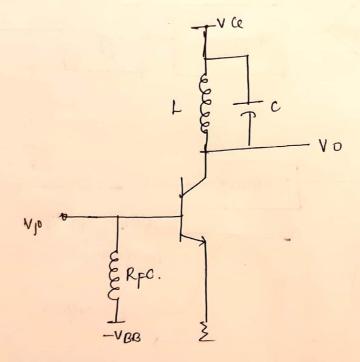

- In Lc oscillator the feed back network employs the LC components to generalle oscillations in radio freeferency hange (100 KH3-100 mH2)

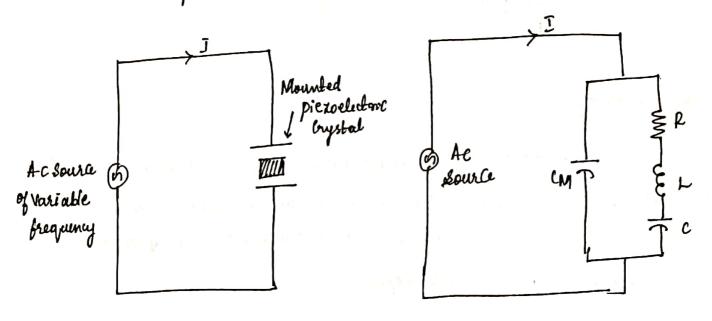

- In Grystal oscillators the feedback network uses prezo elektic Grystal to generate oscillation. Grystal oscillators are used to generate oscillations in the frequency range of (10KHz-10MHz)

### Re phase shift oscillator using FET

- Inophase Shift oscillator Renetural is used in feedback path. In oscicllator feed back network much indroduced phase Shift of 180° to obtain the total phase Shift around a loop as 360 or 0°

- I le phase shift oscillator is a dow frequency oscillator.

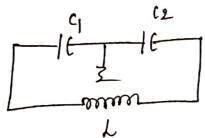

#### Rc feedback network

Feedback network in Rc phase shift excillator.

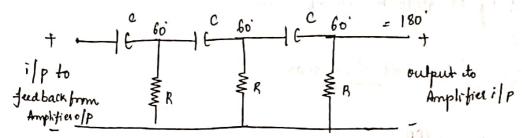

one Rc Network produces phoise shift of 60' Item to produce phoise shift of 180° Ite. network are connected in Series to generate total phase of 180' The n/w is disigned in such a way that all the resistance values are capacitance values are same so that for particular frequency each Section of Rtc produces a phase shift of 60'.

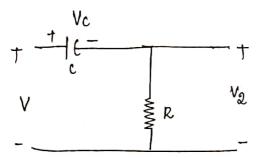

### Consider the Single Rc network

Single Rc Network and phoisor diagram.

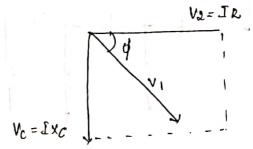

The resistor voltage and averent are in phase 5 in a capacitor the Current Leonds the voltage by an angle 90°. V, 5 V2 differ in phase by angle of

$$tand = \frac{Vc}{V2} = \frac{fxc}{ZR} = \frac{Rc}{R}$$

$$x_c = \frac{1}{Nc} = \frac{1}{2RfC}$$

The values of RSC are selected so as to give a phase shift of 60 at the desired

frequency of oscillations Simu all Mu librer Rc Sections are identical the total phone shift introduced by the feedback network us 120°.

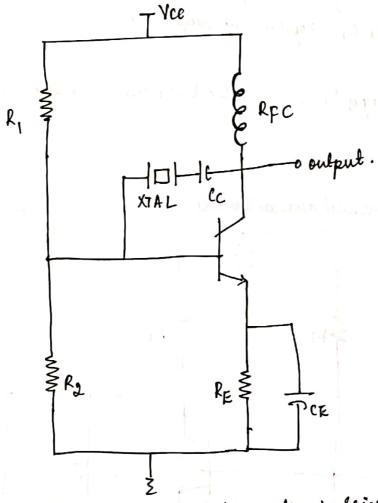

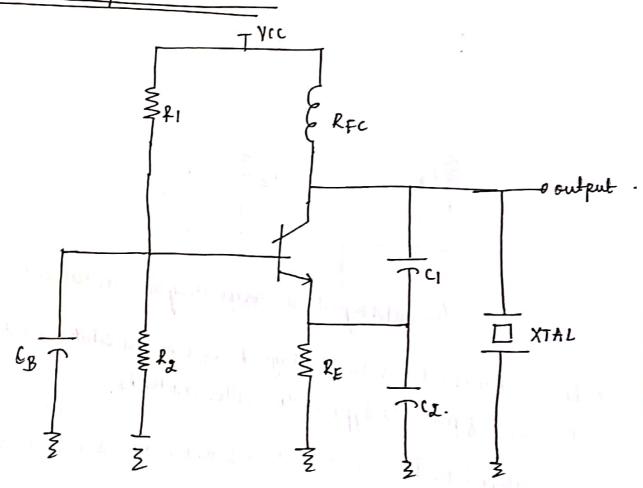

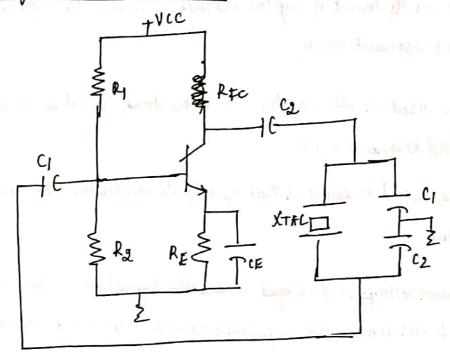

FET phase shift oscillator: CKL diagram

Figure shows the Cacuit of FET Re phase shift oscillator. It Consider of Single Stage amplifred and a feedback network compressing of three identical RC Sections.